## **FUJITSU SEMICONDUCTOR**

CONTROLLER MANUAL

# FR60 32-BIT MICROCONTROLLER MB91301 Series HARDWARE MANUAL

# FR60 32-BIT MICROCONTROLLER MB91301 Series HARDWARE MANUAL

**FUJITSU LIMITED**

#### Objectives and Intended Reader

Thank you for using Fujitsu semiconductor products.

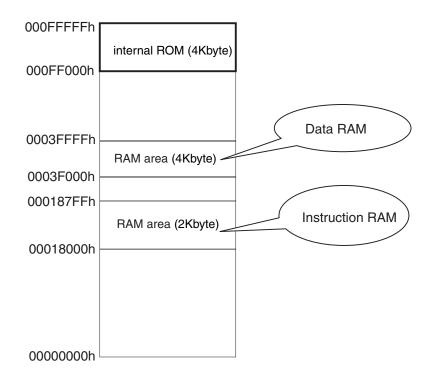

The MB91301 series is a standard microcontroller that has a 32-bit high-performance RISC CPU as well as built-in I/O resources and bus control mechanisms for embedded controller that requires high-performance and high-speed CPU processing. Although the MB91301 series basically uses external bus access to support a vast address space accessed by a 32-bit CPU, it has a 4 KB instruction cache memory and 4 KB RAM (for data) to increase the speed at which the CPU executes instructions.

The MB91301 series is most suitable for embedded applications, such as digital video cameras, navigation systems, and DVD players, that require a high level of CPU processing power.

The MB91301 series is one of the FR60 series of microcontrollers, which are based on the FR30/40 family of CPUs. It has enhanced bus access and is optimized for high-speed use.

This manual is intended for engineers who will develop products using the MB91301 series and describes the functions and operations of the MB91301 series. Read this manual thoroughly.

For more information on instructions, see the "Instructions Manual".

#### Trademarks

FR, which is an abbreviation of FUJITSU RISC controller, is a product of Fujitsu Limited.

#### License

Purchase of Fujitsu  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use, these components in an  $I^2C$  system provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

#### Structure of This Manual

This manual consists of the following 20 chapters and an appendix.

#### CHAPTER 1 OVERVIEW

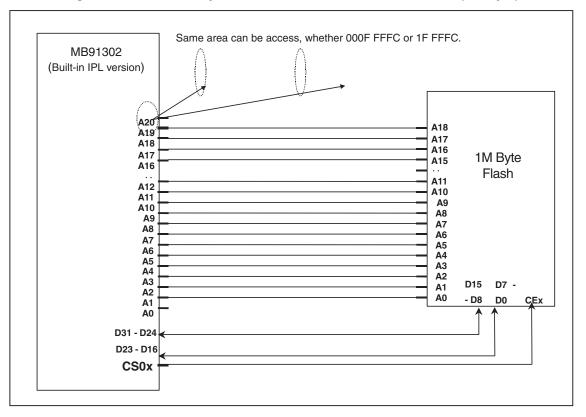

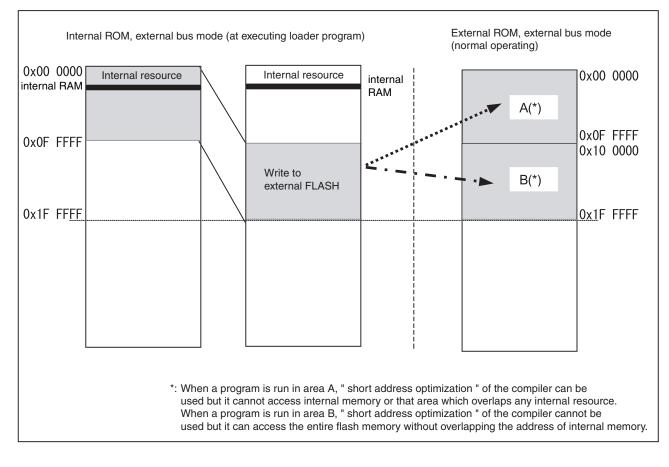

This chapter provides basic information required to understand the MB91301 series, and covers features, a block diagram, and functions.

#### **CHAPTER 2 HANDLING THE DEVICE**

This chapter provides precautions on handling the MB91301 series.

#### **CHAPTER 3 CPU AND CONTROL UNITS**

This chapter provides basic information required to understand the functions of the MB91301 series. It covers architecture, specifications, and instructions.

#### **CHAPTER 4 EXTERNAL BUS INTERFACE**

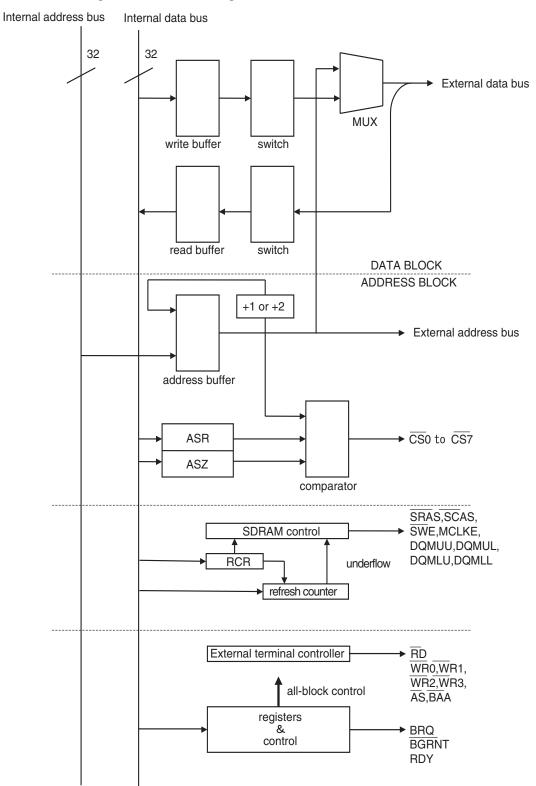

The external bus interface controller controls the interfaces with the internal bus for chips and with external memory and I/O devices.

This chapter explains each function of the external bus interface and its operation.

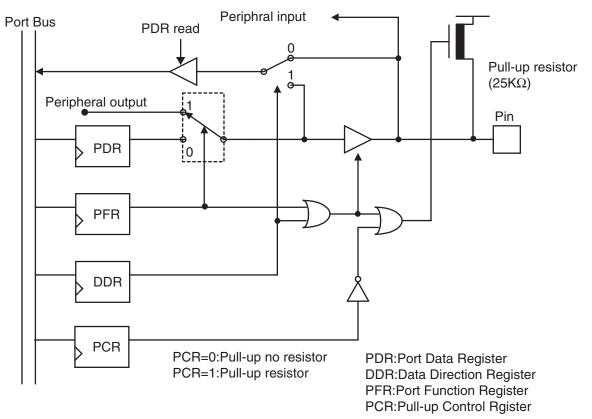

#### CHAPTER 5 I/O PORT

This chapter describes the I/O ports and the configuration and functions of registers.

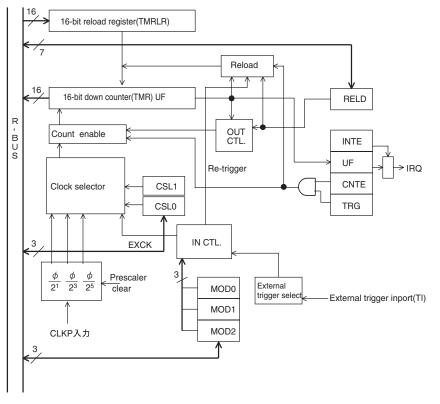

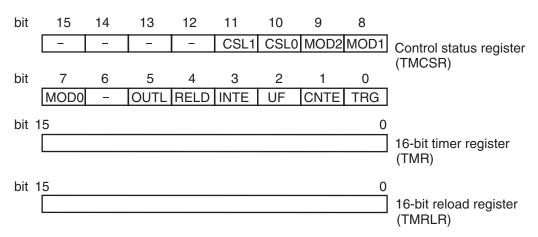

#### CHAPTER 6 16-BIT RELOAD TIMER

This chapter describes the 16-bit reload timer, the configuration and functions of registers, and 16-bit reload timer operation.

#### CHAPTER 7 PPG TIMER

This chapter describes the U-TIMER, the configuration and functions of registers, and U-TIMER operation.

#### **CHAPTER 8 U-TIMER**

This chapter describes the external interrupt and NMI controller, the configuration and functions of registers, and operation of the external interrupt and NMI controller.

#### **CHAPTER 9 EXTERNAL INTERRUPT AND NMI CONTROLLER**

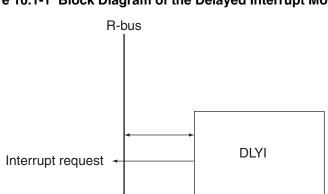

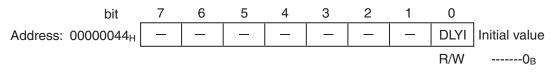

This chapter describes the functions and operation of the delayed interrupt module.

#### CHAPTER 10 DELAYED INTERUPT MODULE

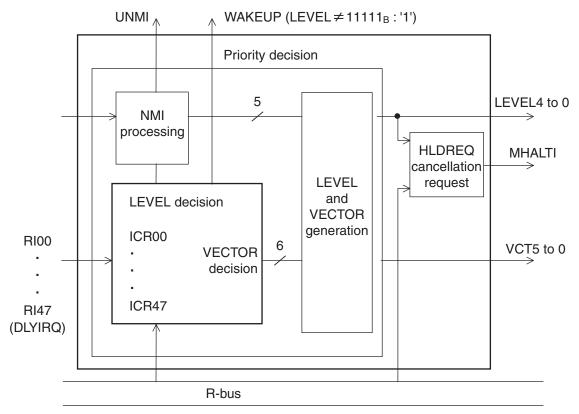

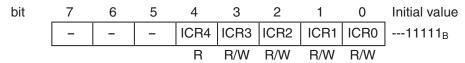

This chapter describes the interrupt controller, the configuration and functions of registers, and interrupt controller operation. It also presents an example of using the hold request cancellation request function.

#### CHAPTER 11 INTERRUPT CONTROLLER

This chapter describes the A/D converter, the configuration and functions of registers, and A/D converter operation.

#### CHAPTER 12 A/D CONVERTER

This chapter describes the UART, the configuration and functions of registers, and UART operation.

#### **CHAPTER 13 UART**

This chapter describes the  $I^2C$  interface, the configuration and functions of registers, and  $I^2C$  interface operation.

#### CHAPTER 14 DMA CONTROLLER (DMAC)

This chapter describes the DMA controller (DMAC), the configuration and functions of registers, and DMAC operation.

#### **CHAPTER 15 BIT SEARCH MODULE**

This chapter describes the bit search module, the configuration and functions of registers, and bit search module operation.

#### CHAPTER 16 I2C INTERFACE

This chapter describes the bit search module, the configuration and functions of registers, and bit search module operation.

#### CHAPTER 17 16-bit Free-run Timer

This chapter describes the bit search module, the configuration and functions of registers, and bit search module operation.

#### **CHAPTER 18** Input Capture

This chapter describes the bit search module, the configuration and functions of registers, and bit search module operation.

#### CHAPTER 19 Program Loader Mode (Supported only by the MB91302A (IPL integrated model))

This chapter describes the bit search module, the configuration and functions of registers, and bit search module operation.

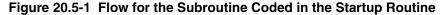

#### CHAPTER 20 Real - time OS Embedded MB91302A - 010 User's Guide

This chapter describes the bit search module, the configuration and functions of registers, and bit search module operation.

#### APPENDIX

This appendix consists of the following parts: I/O map, interrupt vector, pin states in the CPU state, notes on using a little endian area, and instruction lists. The appendix contains detailed information that could not be included in the main text and reference material for programming.

- The contents of this document are subject to change without notice.

- Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage

or loss from such failures by incorporating safety design measures into your facility and equipment such

as redundancy, fire protection, and prevention of over-current levels and other abnormal operating

conditions.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

©2004 FUJITSU LIMITED Printed in Japan

# How To Read This Manual

#### ■ Terms Used in This Manual

The following defines principal terms used in this manual.

| Term   | Meaning                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

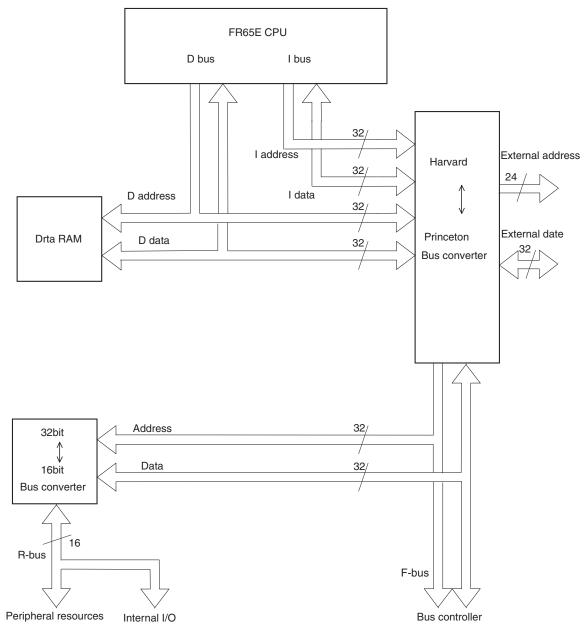

| I-bus  | 32 bit bus for internal instructions. In the FR series, which is based on an internal Harvard architecture, independent buses are used for instructions and data. A bus converter is connected to the I-bus.                                                                                                                                                                                                       |

| D-bus  | Internal 32-bit data bus. An internal resource is connected to the D-bus.                                                                                                                                                                                                                                                                                                                                          |

| F-bus  | Internal instructions and data are multiplexed on a Princeton bus.<br>The F-bus is connected to the I-bus and D-bus via a switch. The F-bus is<br>connected to built-in resources such as ROM and RAM.                                                                                                                                                                                                             |

| X-bus  | External interface bus.<br>The X-bus is connected to the external interface module.<br>Data and instructions are multiplexed on an external bus.                                                                                                                                                                                                                                                                   |

| R-bus  | Internal 16-bit data bus. The R-bus is connected to the F-bus via an adapter. An I-O, clock generator, and interrupt controller are connected to the R-bus. Since addresses and data are multiplexed on an R-bus that is 16 bits wide, more than one cycle is required for the CPU to access these resources.                                                                                                      |

| E-unit | Execution unit for operations.                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKP   | System clock. Clock generated by the clock generator for each of the internal resources connected to the R-bus. This clock has the same frequency as the source oscillation at its maximum, but becomes a 1, 1/2, 1/3, 1/4, 1/5, 1/6, 1/7, or 1/16 (or 1/2, 1/4, 1/6, or 1/32) frequency clock as determined by the divide-by rate specified by the B3 to B0 bits in the clock generator DIVR0 register.           |

| CLKB   | System clock. Operating clock for the CPU and each of the other resources connected to a bus other than the R-bus and X-bus. This clock has the same frequency as the source oscillation at its maximum, but becomes a 1, 1/2, 1/3, 1/4, 1/5, 1/6, 1/7,, 1/16 (or 1/2, 1/4, 1/6,, 1/32) frequency clock as determined by the divided-by rate specified by the P3 to P0 bits in the clock generator DIVR0 register. |

| CLKT   | System clock. Operating clock for the external resources connected to the X-<br>bus.<br>This clock has the same frequency as the source oscillation at its maximum, but<br>becomes a 1, 1/2, 1/3, 1/4, 1/5, 1/6, 1/7,, 1/16 (or 1/2, 1/4, 1/6,, 1/32)<br>frequency clock as determined by the divided-by rate specified by the T3 to T0<br>bits in the clock generator DIVR1 register.                             |

vi

# PREFACE How To Read This Manual

| СНАРТ | ER 1 OVERVIEW                                    | 1    |

|-------|--------------------------------------------------|------|

| 1.1   | Features of the MB91301 Series                   | 2    |

| 1.2   | Block Diagram                                    | 7    |

| 1.3   | External Dimensions                              | 9    |

| 1.4   | Pin Layout                                       | . 11 |

| 1.5   | Pin No. Table                                    | . 13 |

| 1.6   | List of Pin Functions                            | . 15 |

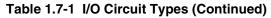

| 1.7   | I/O Circuit Types                                | . 31 |

| СНАРТ | ER 2 HANDLING THE DEVICE                         | 35   |

| 2.1   | Precautions on Handling the Device               | . 36 |

| 2.2   | Precautions on Handling Power Supplies           | . 42 |

| СНАРТ | ER 3 CPU AND CONTROL UNITS                       | 43   |

| 3.1   | Memory Space                                     | . 44 |

| 3.2   | Internal Architecture                            | . 47 |

| 3.3   | Instruction Cache                                | . 52 |

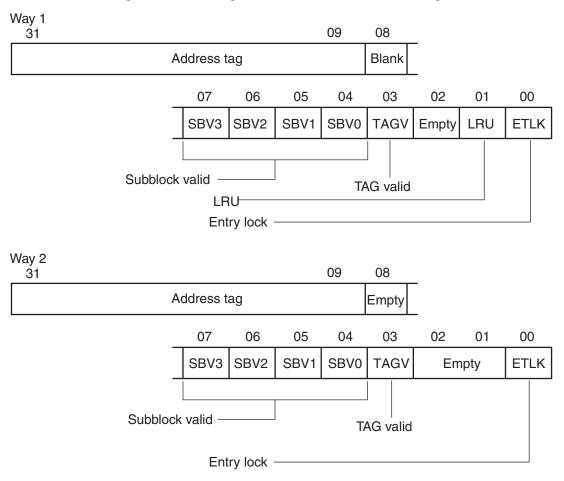

| 3.3.1 | Configuration of the Instruction Cache           | . 53 |

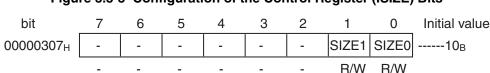

| 3.3.2 | Configuration of the Control Registers           | . 56 |

| 3.3.3 | Instruction Cache Statuses and Settings          | . 60 |

| 3.3.4 | Setting Up the Instruction Cache Before Use      | . 62 |

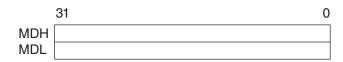

| 3.4   | Dedicated Registers                              |      |

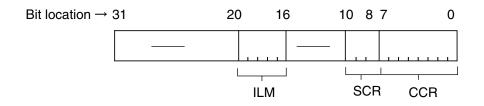

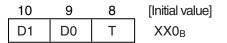

| 3.4.1 | Program Status (PS) Register                     | . 68 |

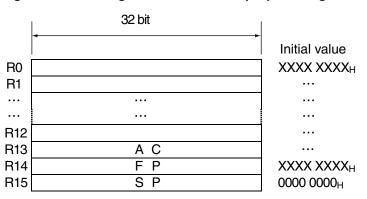

| 3.5   | General-Purpose Registers                        | . 72 |

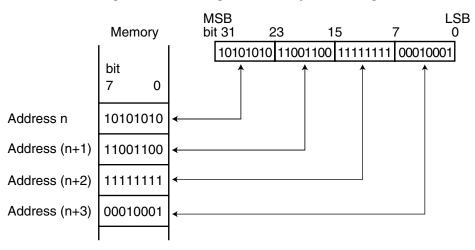

| 3.6   | Data Structure                                   | . 73 |

| 3.7   | Word Alignment                                   | . 74 |

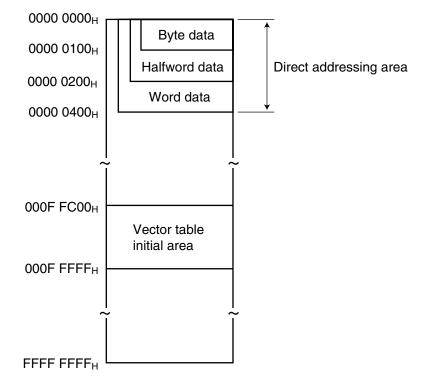

| 3.8   | Memory Map                                       | . 75 |

| 3.9   | Branch Instructions                              | . 76 |

| 3.9.1 | Operation of Branch Instructions with Delay Slot | . 77 |

| 3.9.2 |                                                  |      |

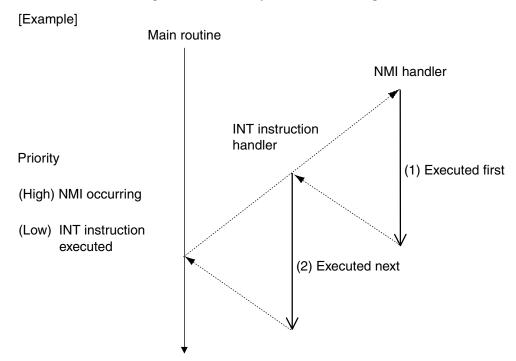

| 3.10  | EIT (Exception, Interrupt, and Trap)             | . 81 |

| 3.10  | 1 EIT Interrupt Levels                           | . 82 |

| 3.10  | 2 Interrupt Control Register (ICR)               | . 84 |

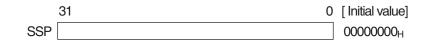

| 3.10  | 3 System Stack Pointer(SSP)                      | . 85 |

| 3.10  | 4 Table Base Register (TBR)                      | . 86 |

| 3.10  | 5 Multiple EIT Processing                        | . 90 |

| 3.10  | 6 EIT Operations                                 | . 92 |

| 3.11  | Reset (Device Initialization)                    | . 96 |

| 3.11  | 1 Reset Levels                                   | . 97 |

| 3.11  | 2 Reset Sources                                  | . 98 |

| 3.11  | 3 Reset Sequence                                 | 100  |

| 3.11  | 4 Oscillation Stabilization Wait Time            | 101  |

| 3.11  | 5 Reset Operation Modes                          | 103  |

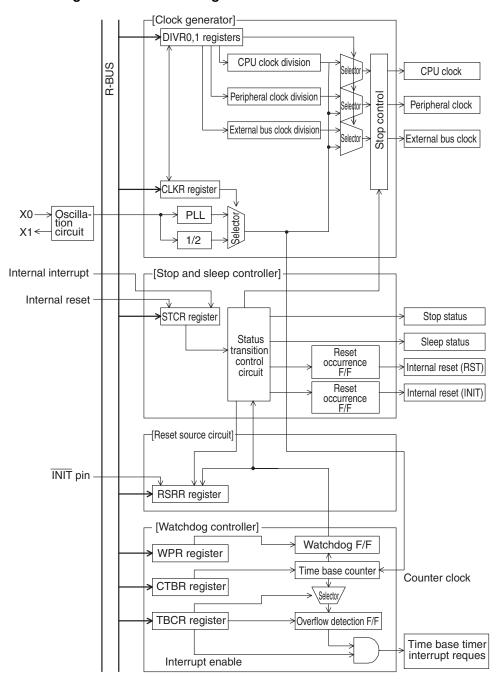

| 3.12   | Clock Generation Control                                                 | . 105 |

|--------|--------------------------------------------------------------------------|-------|

| 3.12.1 | PLL Controls                                                             | . 106 |

| 3.12.2 | Oscillation Stabilization Wait Time and PLL Lock Wait Time               | . 108 |

| 3.12.3 | Clock Distribution                                                       | . 110 |

| 3.12.4 | Clock Division                                                           | . 112 |

| 3.12.5 | Block Diagram of Clock Generation Controller                             | . 113 |

| 3.12.6 | Register of Clock Generation Controller                                  | 114   |

| 3.12.7 | Peripheral Circuits of Clock Controller                                  | . 128 |

| 3.13   | Device State Control                                                     | . 131 |

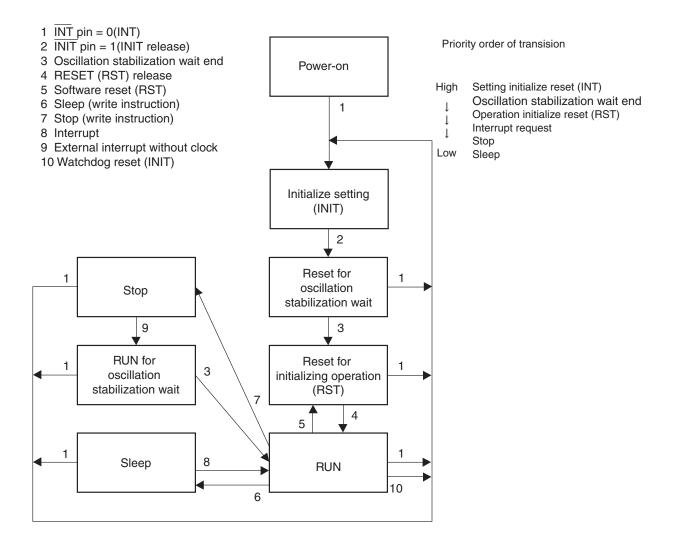

| 3.13.1 | Device States and State Transitions                                      | 133   |

| 3.13.2 | Low-power Modes                                                          | 136   |

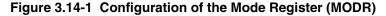

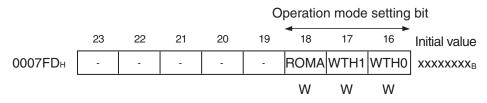

| 3.14   | Operating Modes                                                          | . 140 |

|        |                                                                          |       |

| CHAPTE | R 4 EXTERNAL BUS INTERFACE                                               | 143   |

| 4.1    | Overview of the External Bus Interface                                   | 144   |

| 4.2    | External Bus Interface Registers                                         | 149   |

| 4.2.1  | Area Select Registers 0-7(ASR0-7)                                        | 150   |

| 4.2.2  | Area Configuration Registers 0-7 (ACR0-7)                                | 152   |

| 4.2.3  | Area Wait Register (AWR0-7)                                              |       |

| 4.2.4  | Memory setting register (MCRA for SDRAM/FCRAM auto - precharge OFF mode) |       |

| 4.2.5  | Memory setting register (MCRB for FCRAM auto - precharge ON mode)        |       |

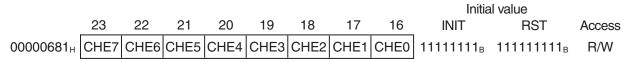

| 4.2.6  | I/O Wait Registers for DMAC (IOWR0, 1)                                   | 170   |

| 4.2.7  | Chip Select Enable Register (CSER)                                       |       |

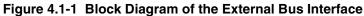

| 4.2.8  | Cache Enable Register (CHER)                                             |       |

| 4.2.9  | Pin/Timing Control Register (TCR)                                        |       |

| 4.2.10 |                                                                          |       |

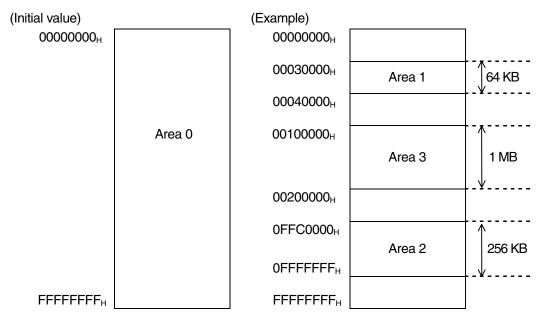

| 4.3    | Setting Example of the Chip Select Area                                  |       |

|        | Endian and Bus Access                                                    |       |

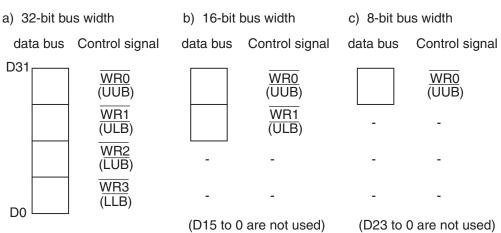

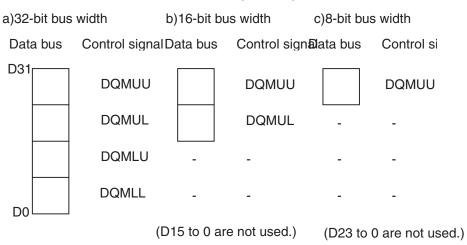

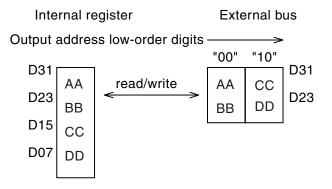

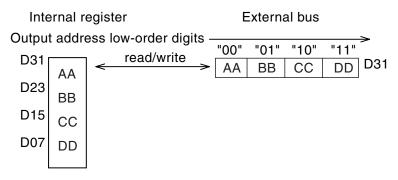

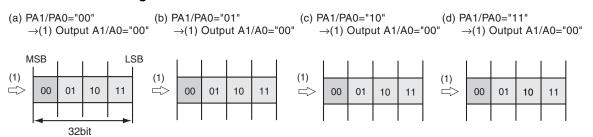

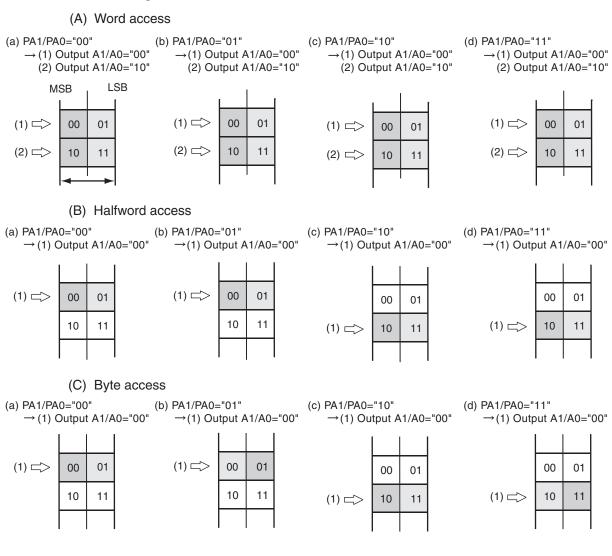

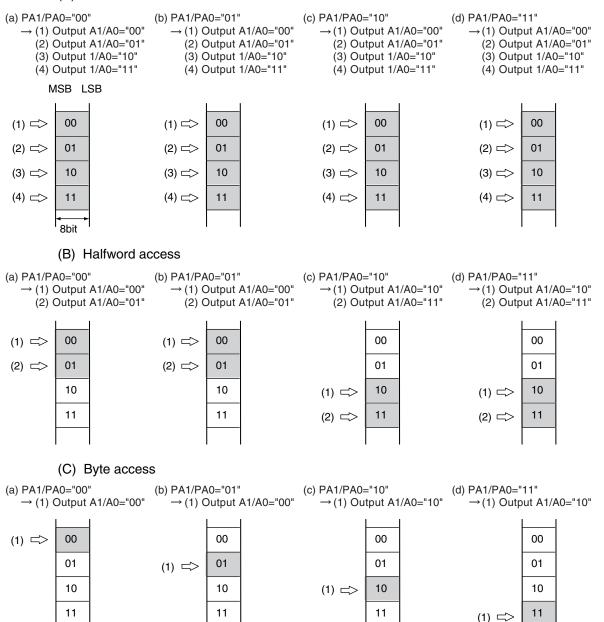

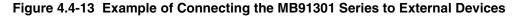

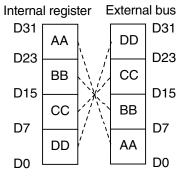

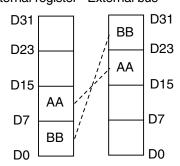

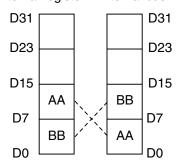

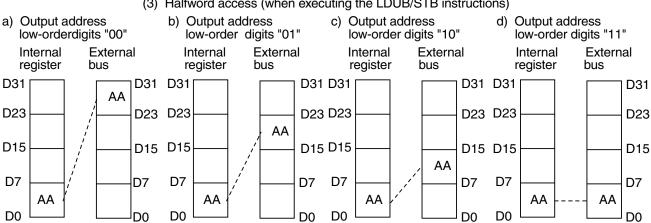

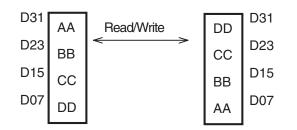

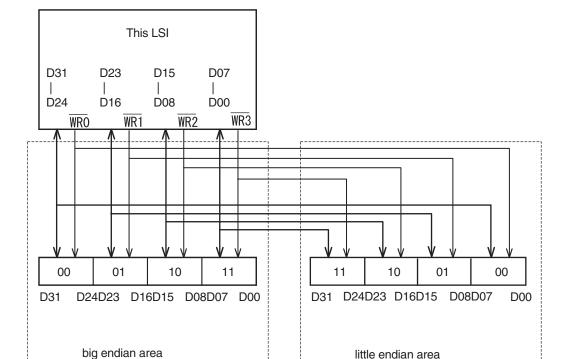

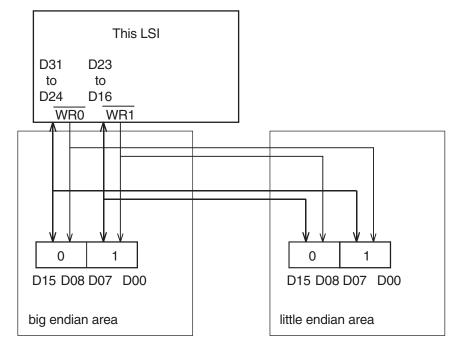

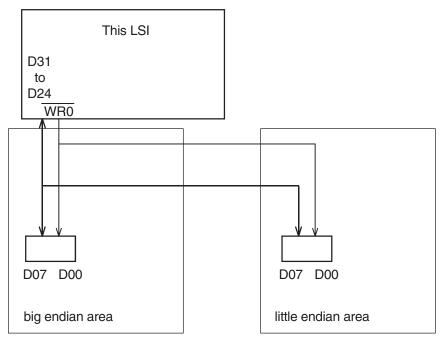

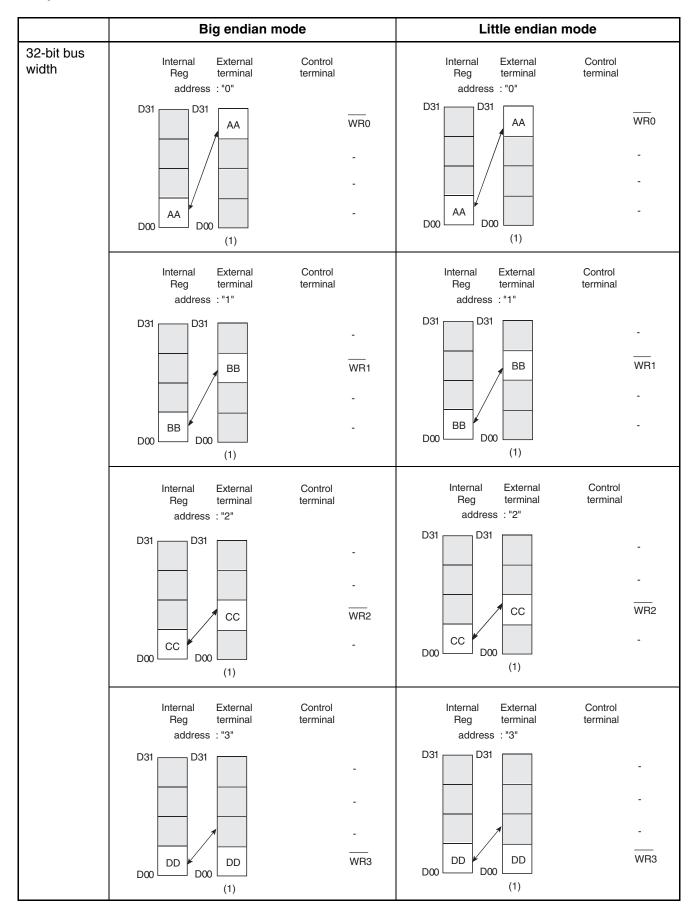

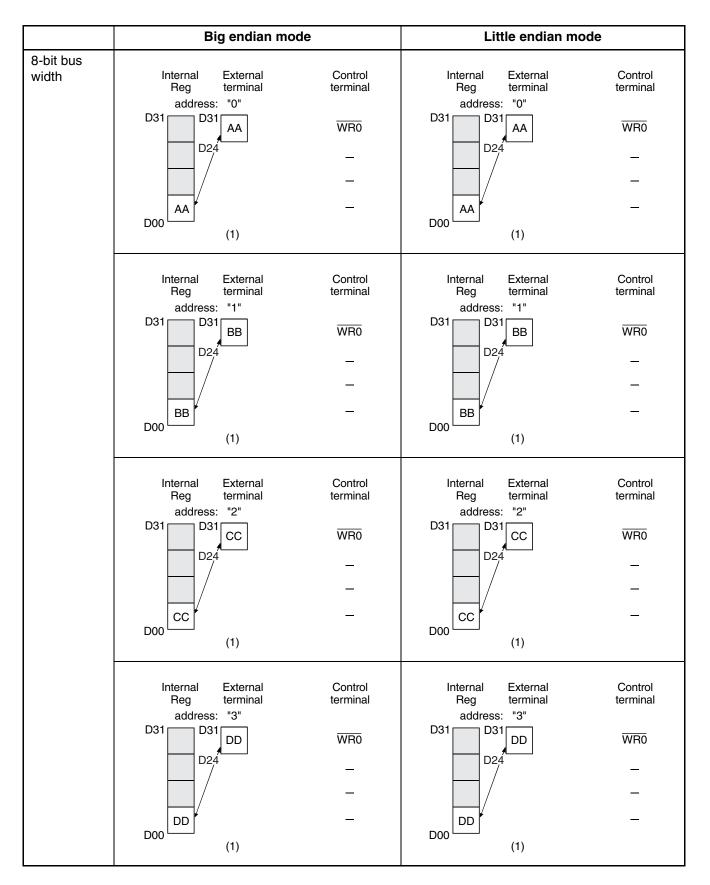

| 4.4.1  | Big Endian Bus Access                                                    | 185   |

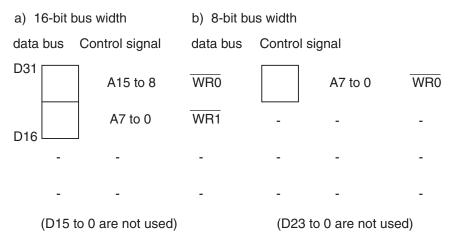

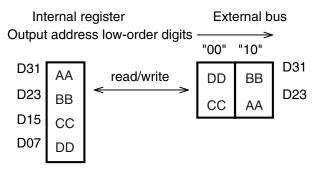

| 4.4.2  | Little Endian Bus Access                                                 | . 192 |

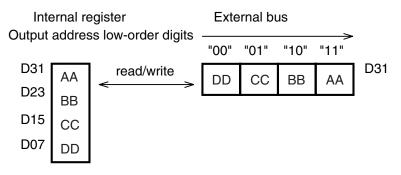

| 4.4.3  | Comparison of Big Endian and Little Endian External Access               | 197   |

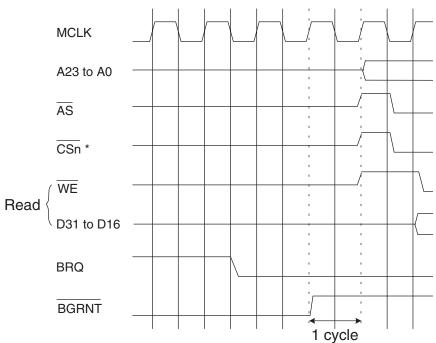

| 4.5    | Operation of the Ordinary bus interface                                  |       |

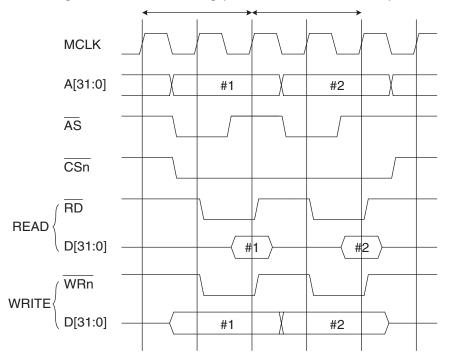

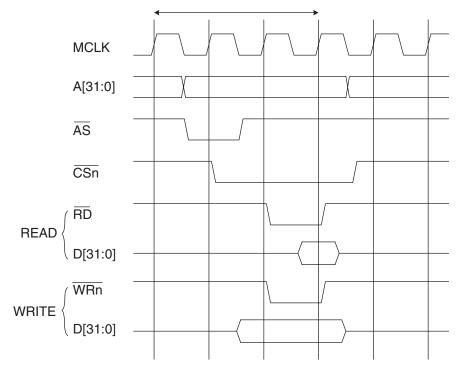

| 4.5.1  | Basic Timing                                                             | 204   |

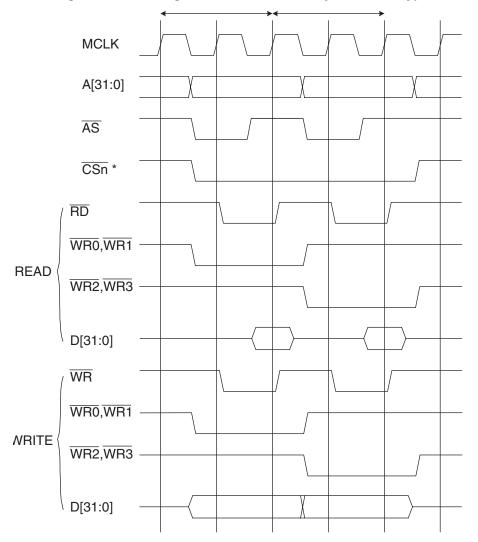

| 4.5.2  | Operation of WRn + Byte Control Type                                     |       |

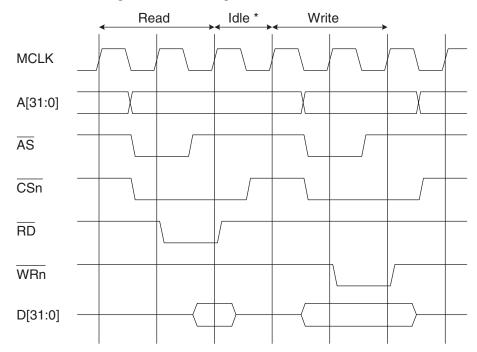

| 4.5.3  | Read -> Write Operation                                                  | . 207 |

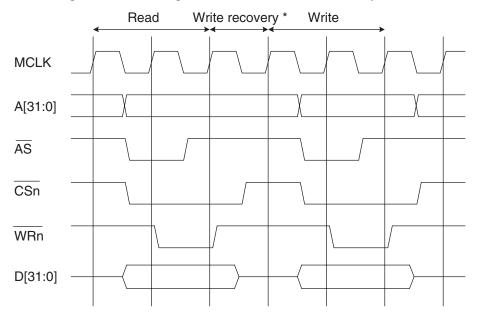

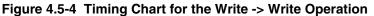

| 4.5.4  | Write -> Write Operation                                                 | . 208 |

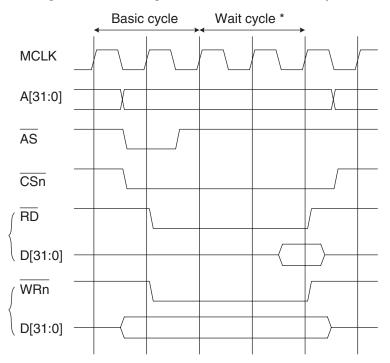

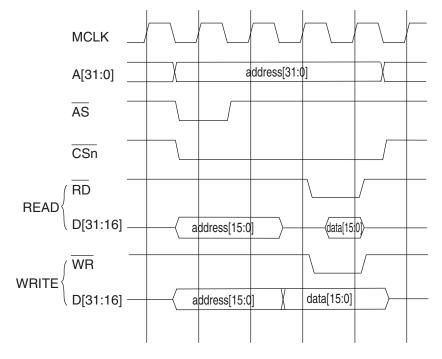

| 4.5.5  | Auto-Wait Cycle                                                          | . 209 |

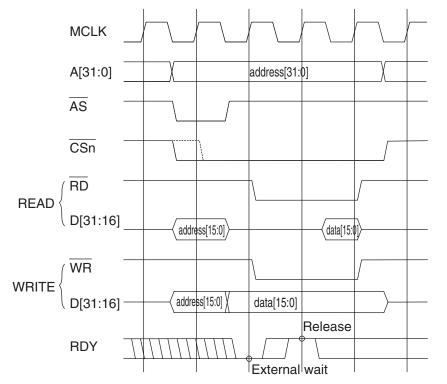

| 4.5.6  | External Wait Cycle                                                      | . 210 |

| 4.5.7  | Synchronous Write Enable Output                                          |       |

| 4.5.8  | CSn Delay Setting                                                        |       |

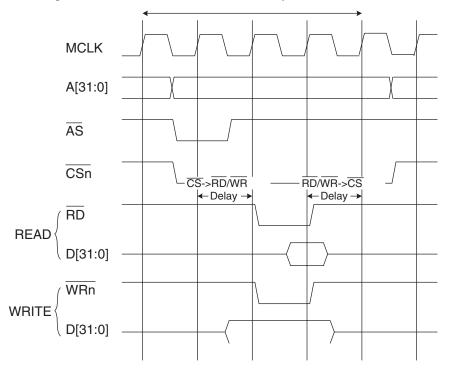

| 4.5.9  | CSn -> RD/WRn Setup and RD/WRn -> CSn Hold Setting                       |       |

| 4.5.10 |                                                                          |       |

| 4.5.11 |                                                                          |       |

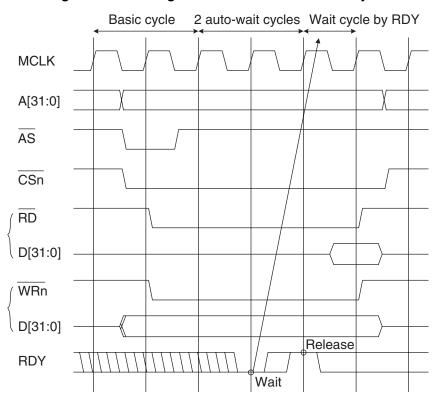

| 4.6    | Burst Access Operation                                                   |       |

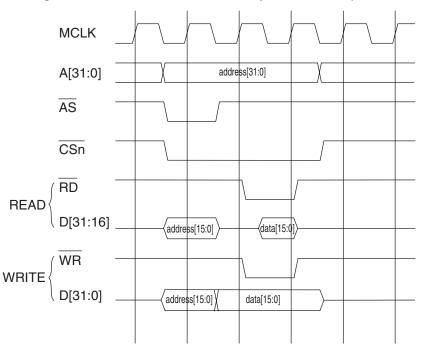

|        | Address/data Multiplex Interface                                         |       |

|        | Prefetch Operation                                                       |       |

|        | SDRAM/FCRAM Interface Operation                                          |       |

|        |                                                                          |       |

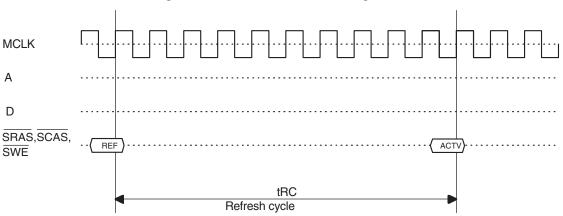

| 4                              | 1.9.1                                                    | Self Refresh                                                                                                                                                                                                    | 229                                                  |

|--------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 4                              | 1.9.2                                                    | Power-on Sequence                                                                                                                                                                                               | 230                                                  |

| 4                              | 1.9.3                                                    | Connecting SDRAM/FCRAM to Many Areas                                                                                                                                                                            | 231                                                  |

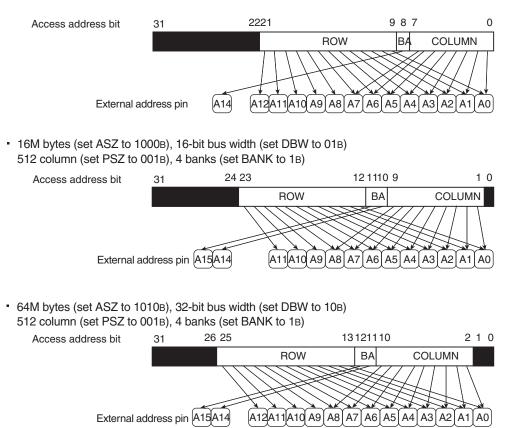

| 4                              | 1.9.4                                                    | Address Multiplexing Format                                                                                                                                                                                     | 232                                                  |

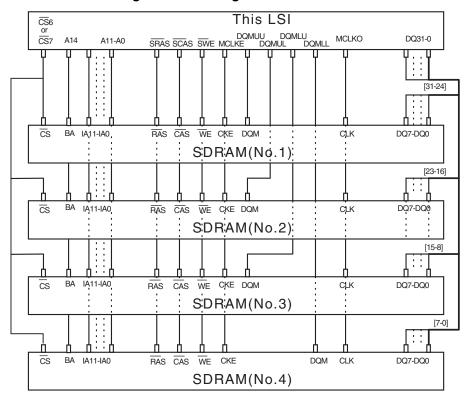

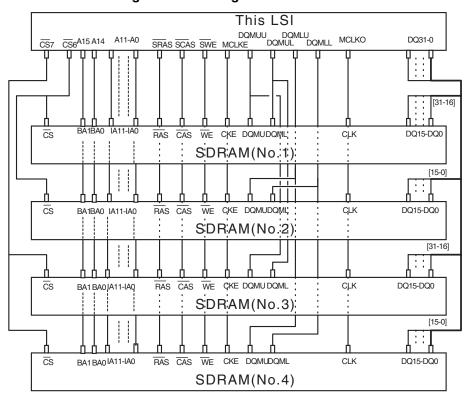

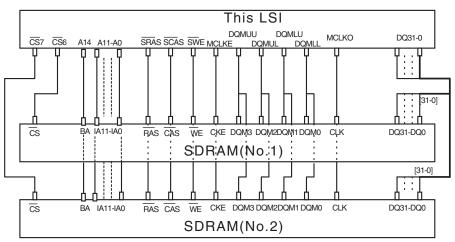

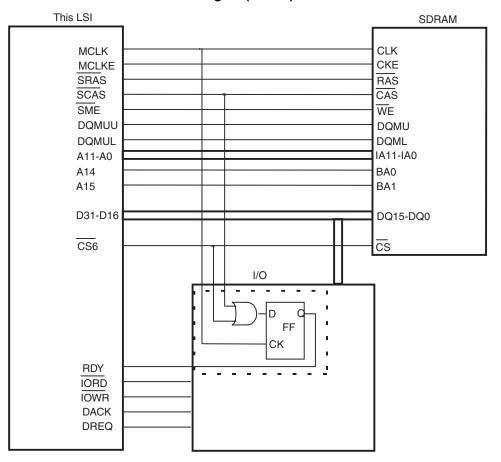

| 4                              | 1.9.5                                                    | Memory Connection Example                                                                                                                                                                                       | 234                                                  |

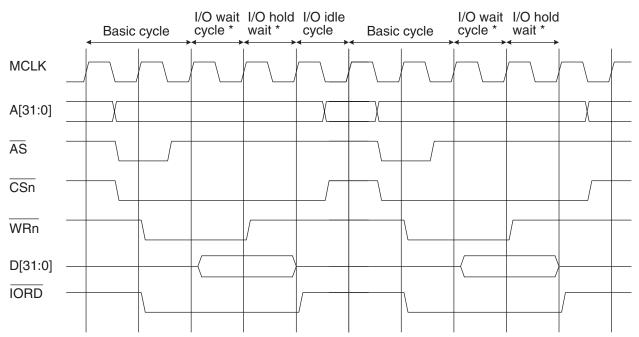

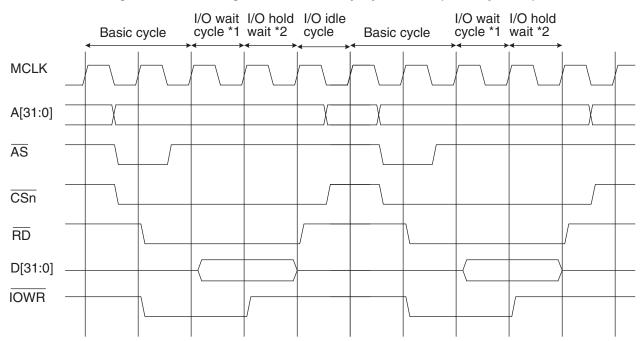

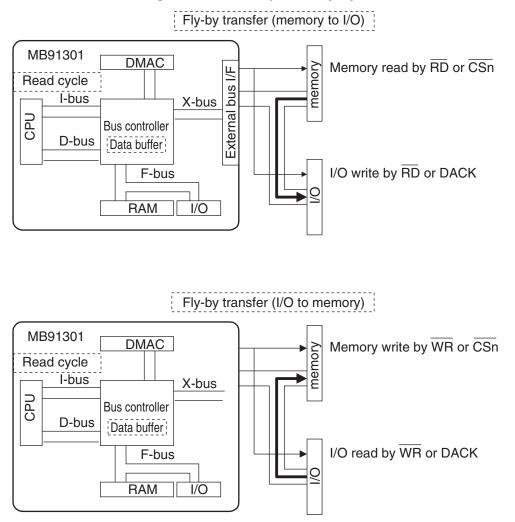

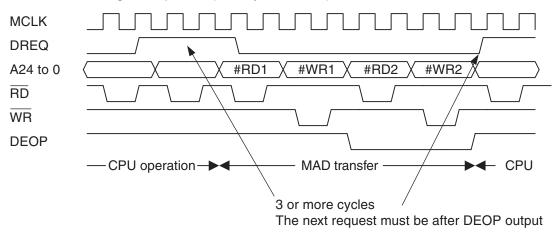

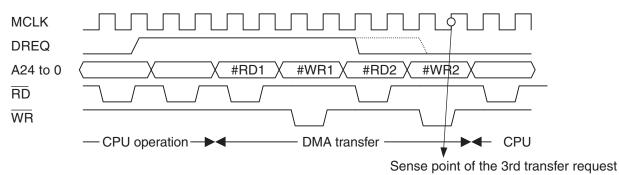

| 4.1                            | 10                                                       | DMA Access Operation                                                                                                                                                                                            | 237                                                  |

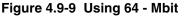

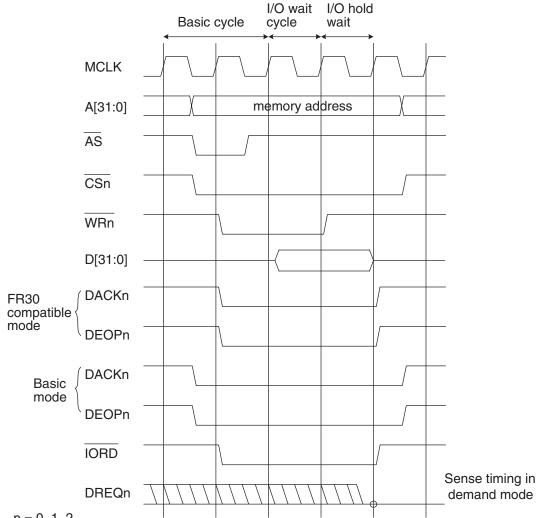

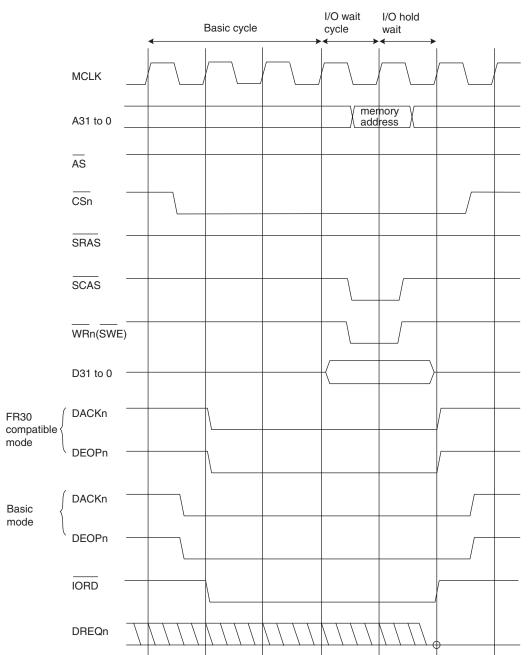

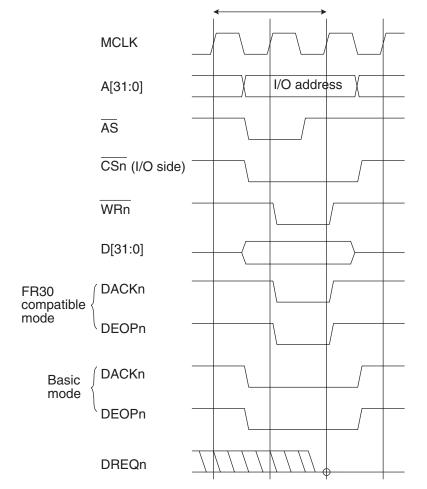

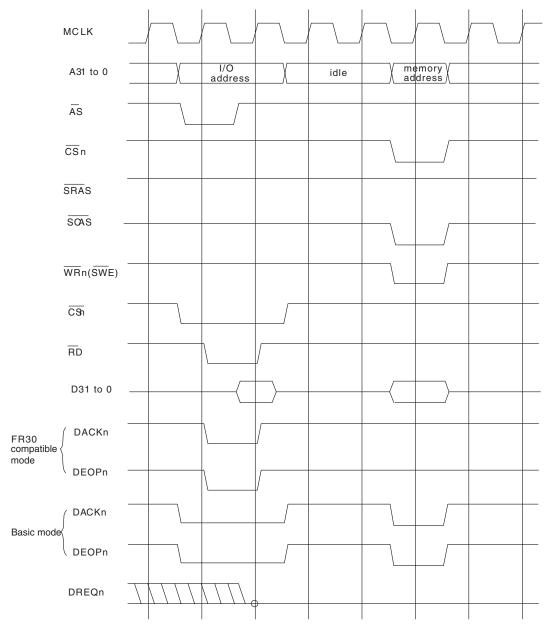

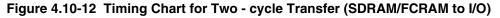

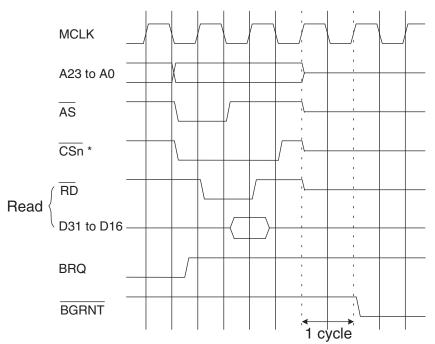

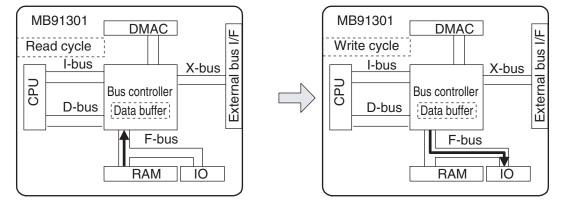

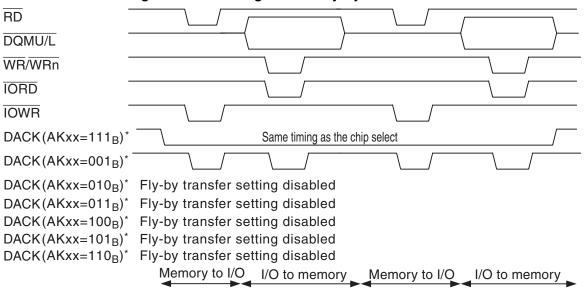

| 4                              | l.10.1                                                   | DMA Fly-By Transfer (I/O -> Memory)                                                                                                                                                                             | 238                                                  |

| 4                              | 1.10.2                                                   | 2 DMA Fly-By Transfer (Memory -> I/O)                                                                                                                                                                           | 240                                                  |

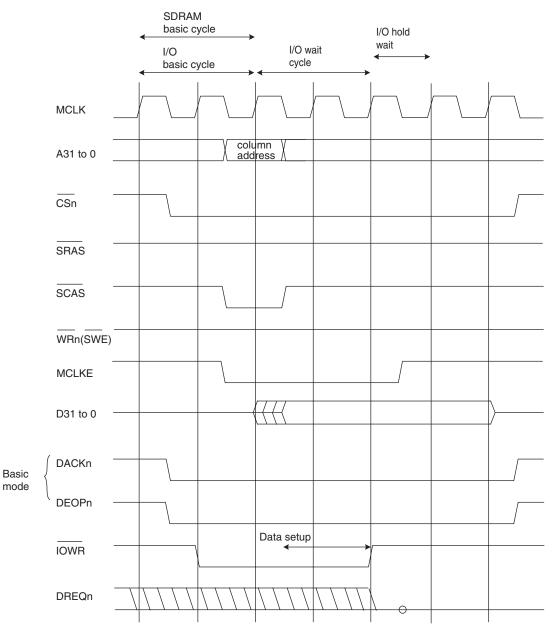

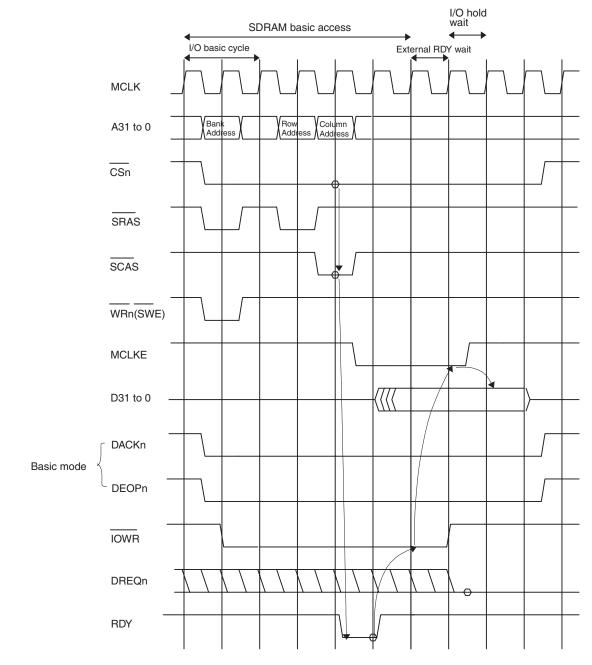

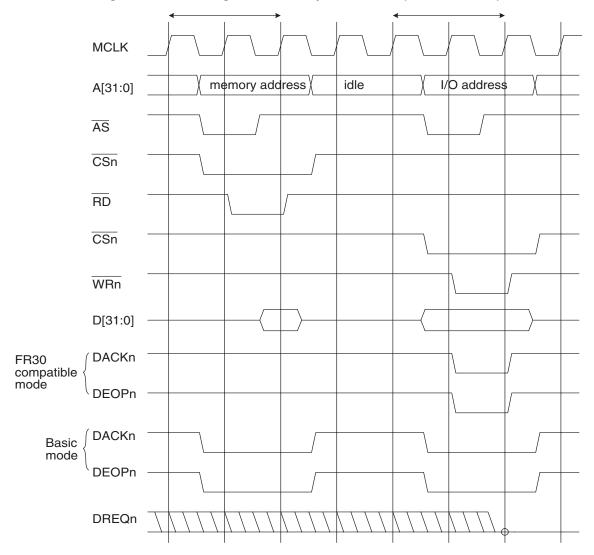

| 4                              | 1.10.3                                                   | B DMA Fly-By Transfer (I/O -> SDRAM/FCRAM)                                                                                                                                                                      | 242                                                  |

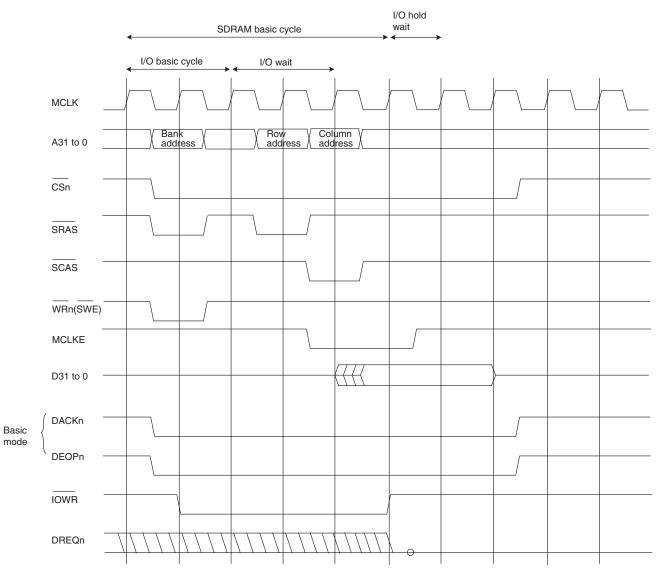

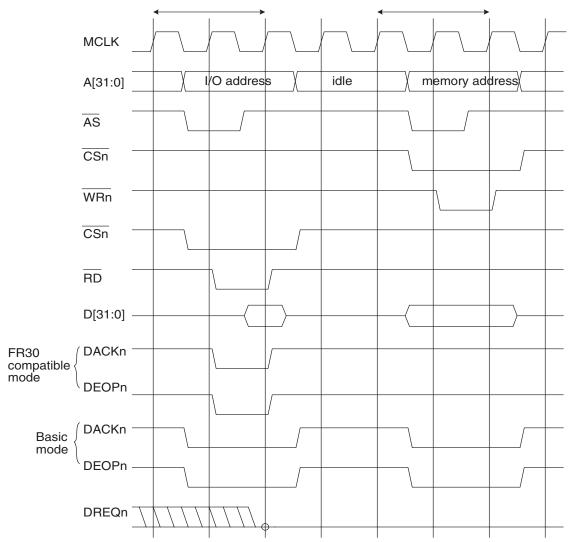

| 4                              | l.10.4                                                   | DMA Fly-By Transfer (SDRAM/FCRAM -> I/O)                                                                                                                                                                        | 244                                                  |

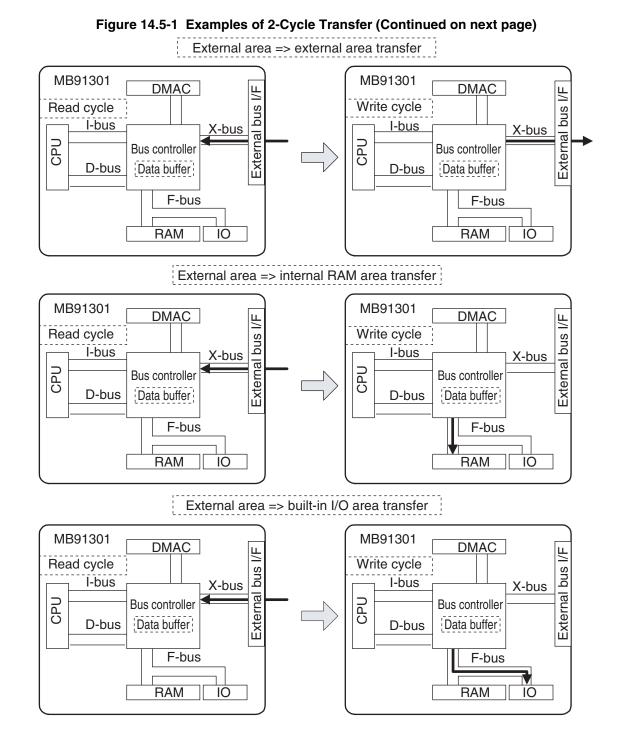

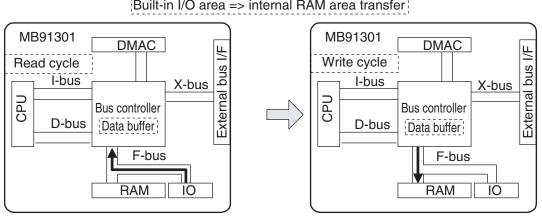

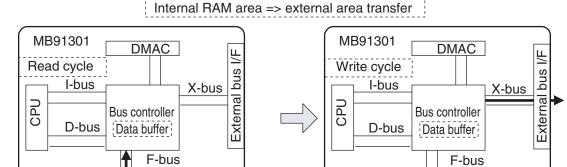

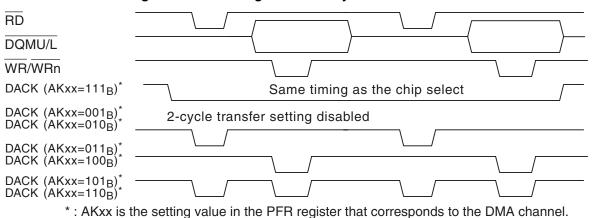

| 4                              | 1.10.5                                                   | 5 2-Cycle Transfer (Internal RAM -> External I/O, RAM)                                                                                                                                                          | 248                                                  |

| 4                              | 1.10.6                                                   | 2-Cycle Transfer (External -> I/O)                                                                                                                                                                              | 249                                                  |

| 4                              | l.10.7                                                   | 2-Cycle Transfer (I/O -> External)                                                                                                                                                                              | 250                                                  |

| 4                              | 1.10.8                                                   | 3 2-Cycle Transfer (I/O -> SDRAM/FCRAM)                                                                                                                                                                         | 251                                                  |

| 4                              | 1.10.9                                                   |                                                                                                                                                                                                                 |                                                      |

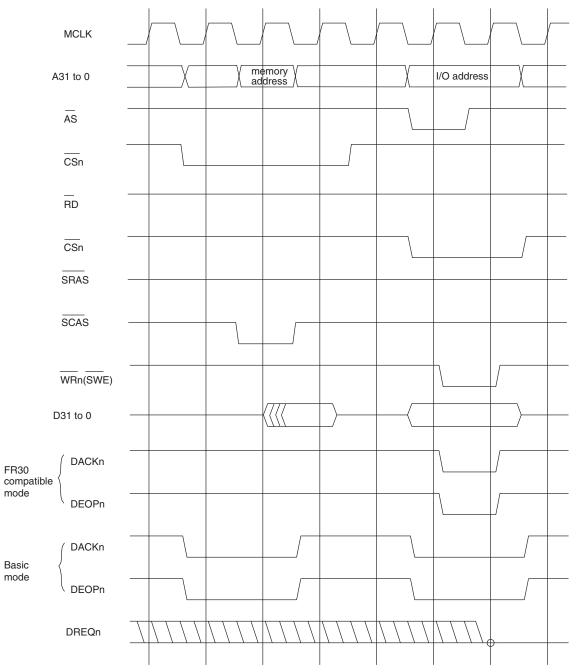

| 4.1                            | 11                                                       | Bus Arbitration                                                                                                                                                                                                 | 254                                                  |

| 4.1                            | 12                                                       | Procedure for Setting a Register                                                                                                                                                                                | 256                                                  |

| 4.1                            |                                                          | Notes on Using the External Bus Interface                                                                                                                                                                       |                                                      |

|                                |                                                          | 5                                                                                                                                                                                                               |                                                      |

| СНА                            | PTE                                                      | R 5 I/O PORT                                                                                                                                                                                                    | 259                                                  |

| 5.1                            |                                                          | Overview of the I/O Port                                                                                                                                                                                        |                                                      |

| 5.2                            |                                                          | I/O Port Registers                                                                                                                                                                                              |                                                      |

|                                |                                                          |                                                                                                                                                                                                                 |                                                      |

| СНА                            | PTE                                                      | R 6 16-BIT RELOAD TIMER                                                                                                                                                                                         | 271                                                  |

| 6.1                            | 1                                                        | Overview of the 16-bit Reload Timer                                                                                                                                                                             | 272                                                  |

| 6.2                            | 2                                                        | 16-bit Reload Timer Registers                                                                                                                                                                                   | 273                                                  |

| 6                              | 5.2.1                                                    | Control Status Register (TMCSR)                                                                                                                                                                                 |                                                      |

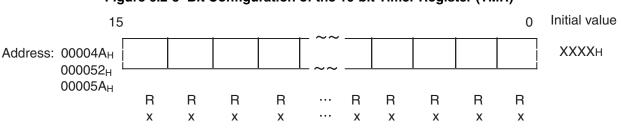

| 6                              | 5.2.2                                                    | 16-bit Timer Register (TMR)                                                                                                                                                                                     |                                                      |

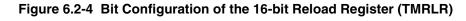

| 6                              | 5.2.3                                                    | 16-bit Reload Register (TMRLR)                                                                                                                                                                                  | 278                                                  |

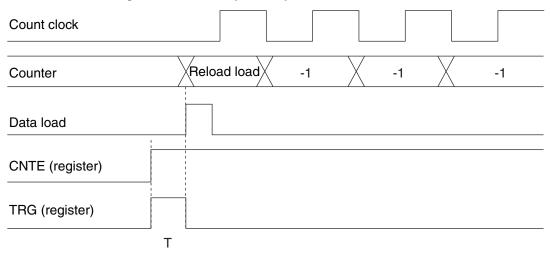

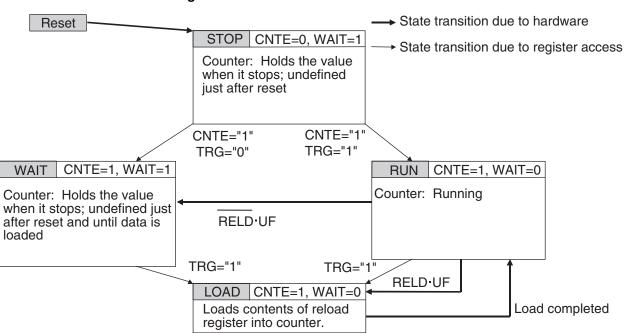

| 6.3                            | 3                                                        | 16-bit Reload Timer Operation                                                                                                                                                                                   |                                                      |

| 6.4                            | 1                                                        | Operating States of the Counter                                                                                                                                                                                 |                                                      |

| 6.5                            |                                                          | Precautions on Using the 16-bit Reload Timer                                                                                                                                                                    |                                                      |

|                                |                                                          |                                                                                                                                                                                                                 |                                                      |

| СНА                            | PTE                                                      | R 7 PPG TIMER                                                                                                                                                                                                   | 283                                                  |

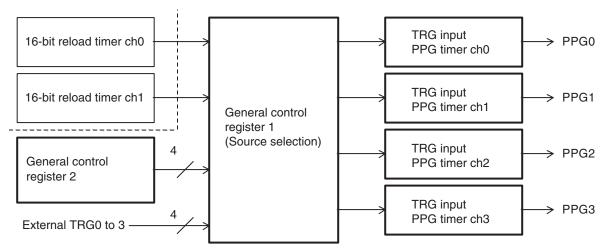

| 7.1                            | 1                                                        | Overview of PPG Timer                                                                                                                                                                                           | 284                                                  |

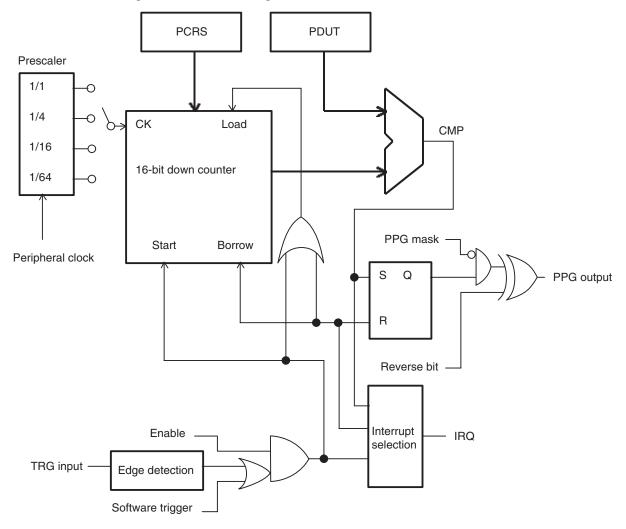

| 7.2                            |                                                          | Block Diagram of PPG Timer                                                                                                                                                                                      |                                                      |

| 7.3                            |                                                          | Registers of PPG Timer                                                                                                                                                                                          |                                                      |

|                                | -                                                        | -                                                                                                                                                                                                               |                                                      |

|                                | 7.3.1                                                    | Control status registers (PCNH, PCNL)                                                                                                                                                                           | 288                                                  |

|                                | 7.3.1<br>7.3.2                                           | Control status registers (PCNH, PCNL)                                                                                                                                                                           |                                                      |

| 7                              | 7.3.2                                                    | PPG cycle set register (PCSR)                                                                                                                                                                                   | 292                                                  |

| 7<br>7                         | 7.3.2<br>7.3.3                                           | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)                                                                                                                                                   | 292<br>293                                           |

| 7<br>7<br>7                    | 7.3.2<br>7.3.3<br>7.3.4                                  | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)<br>PPG timer register (PTMR)                                                                                                                      | 292<br>293<br>294                                    |

| 7<br>7<br>7<br>7               | 7.3.2<br>7.3.3<br>7.3.4<br>7.3.5                         | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)<br>PPG timer register (PTMR)<br>General control register 10 (GCN10)                                                                               | 292<br>293<br>294<br>295                             |

| 7<br>7<br>7<br>7<br>7          | 7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6                | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)<br>PPG timer register (PTMR)<br>General control register 10 (GCN10)<br>General control register 20 (GCN20)                                        | 292<br>293<br>294<br>295<br>298                      |

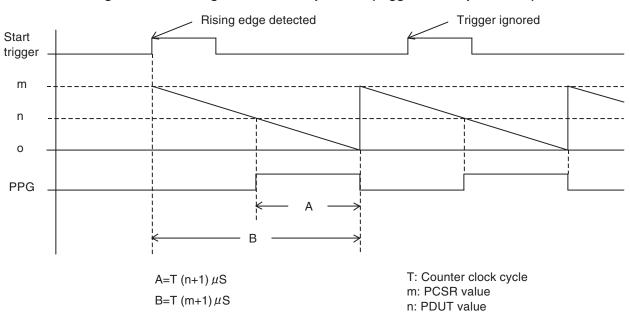

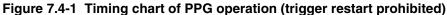

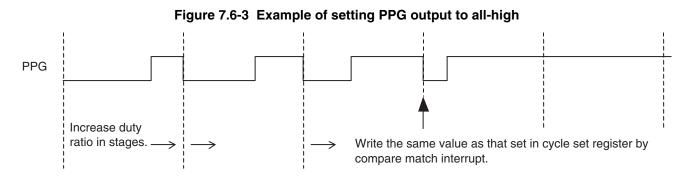

| 7<br>7<br>7<br>7<br>7<br>7.4   | 7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>4           | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)<br>PPG timer register (PTMR)<br>General control register 10 (GCN10)<br>General control register 20 (GCN20)<br>PPG Operation                       | 292<br>293<br>294<br>295<br>298<br>299               |

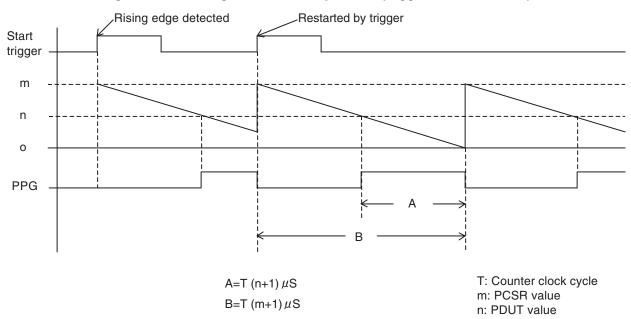

| 7<br>7<br>7<br>7<br>7          | 7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>4<br>5      | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)<br>PPG timer register (PTMR)<br>General control register 10 (GCN10)<br>General control register 20 (GCN20)<br>PPG Operation<br>One-shot Operation | 292<br>293<br>294<br>295<br>298<br>299<br>301        |

| 7<br>7<br>7<br>7<br>7.4<br>7.5 | 7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>4<br>5<br>5 | PPG cycle set register (PCSR)<br>PPG duty set register (PDUT)<br>PPG timer register (PTMR)<br>General control register 10 (GCN10)<br>General control register 20 (GCN20)<br>PPG Operation                       | 292<br>293<br>294<br>295<br>298<br>299<br>301<br>303 |

| 7.8  | Notes   | on Use of the PPG Timer                                            | 307 |

|------|---------|--------------------------------------------------------------------|-----|

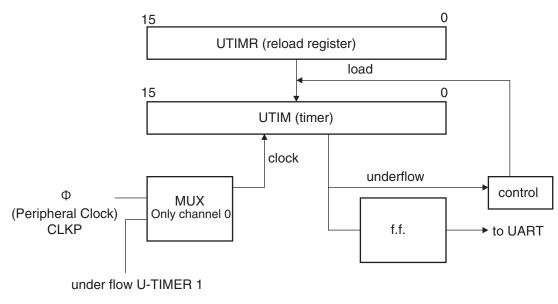

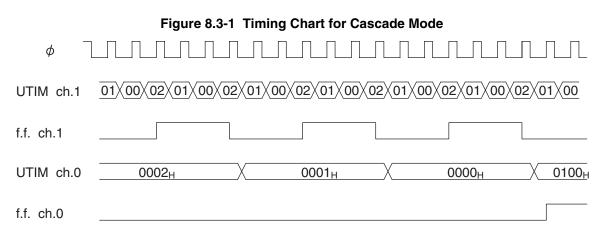

| СНАР | TER 8   | U-TIMER                                                            | 309 |

| 8.1  | Overv   | iew of the U-TIMER                                                 |     |

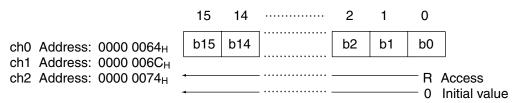

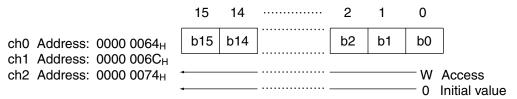

| 8.2  | U-TIM   | ER Registers                                                       |     |

| 8.3  | U-TIM   | ER Operation                                                       | 315 |

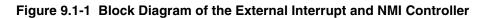

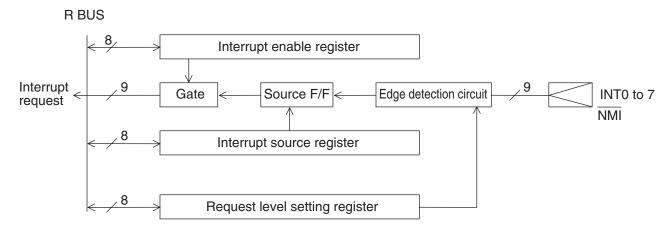

| СНАР | TER 9   | EXTERNAL INTERRUPT AND NMI CONTROLLER                              | 317 |

| 9.1  | Overv   | iew of the External Interrupt and NMI Controller                   |     |

| 9.2  | Exterr  | nal Interrupt and NMI Controller Registers                         |     |

| 9.2  | .1 Inte | errupt Enable Register (ENIR)                                      |     |

| 9.2  | .2 Ex   | ternal Interrupt Source Register (EIRR)                            |     |

| 9.2  | .3 Ex   | ternal Interrupt Request Level Setting Register (ELVR)             |     |

| 9.3  | Opera   | tion of the External Interrupt and NMI Controller                  | 323 |

| СНАР | TER 10  | DELAYED INTERUPT MODULE                                            | 327 |

| 10.1 | Overv   | iew of the Delayed Interrupt Module                                |     |

| 10.2 |         | ed Interrupt Module Registers                                      |     |

| 10.3 | -       | tion of the Delayed Interrupt Module                               |     |

| СНАР | TER 11  | INTERRUPT CONTROLLER                                               | 331 |

| 11.1 | Overv   | iew of the Interrupt Controller                                    |     |

| 11.2 |         | upt Controller Registers                                           |     |

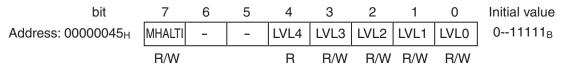

| 11.: |         | errupt Control Register (ICR)                                      |     |

| 11.: |         | Id Request Cancellation Request Level Setting Register (HRCL)      |     |

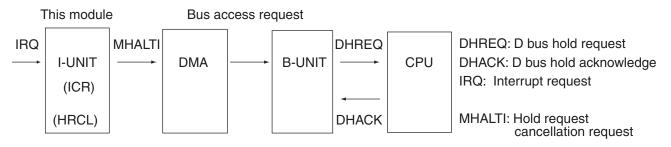

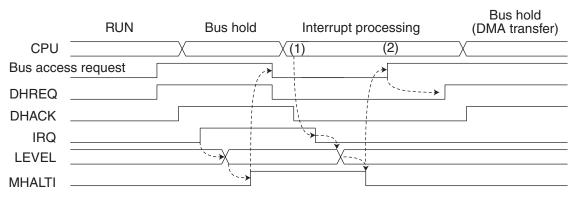

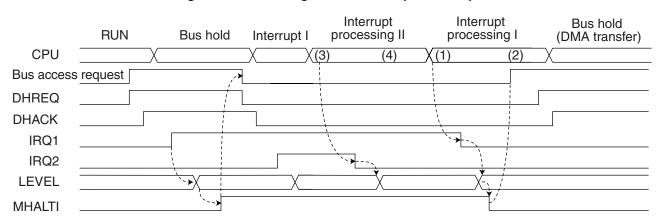

| 11.3 |         | upt Controller Operation                                           |     |

| 11.4 |         | ple of Using the Hold Request Cancellation Request Function (HRCR) |     |

| CHAP | TER 12  | A/D CONVERTER                                                      | 347 |

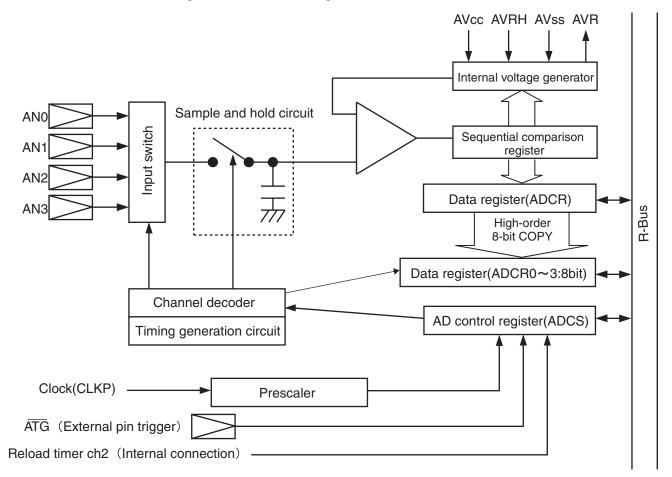

| 12.1 | Overv   | iew of the A/D Converter                                           |     |

| 12.2 |         | onverter Registers                                                 |     |

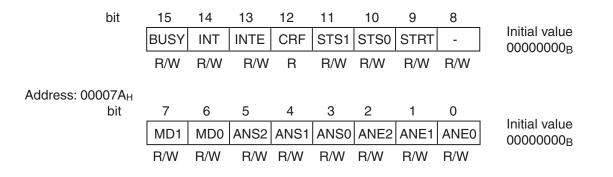

| 12.  |         | ntrol Status Register (ADCS)                                       |     |

| 12.  |         | ta Register (ADCR)                                                 |     |

|      |         | nversion result register (ADCR0 to 3)                              |     |

| 12.3 |         | onverter Operation                                                 |     |

| 12.4 |         | utions on the Using A/D Converter                                  |     |

| CHAP | TER 13  | UART                                                               | 361 |

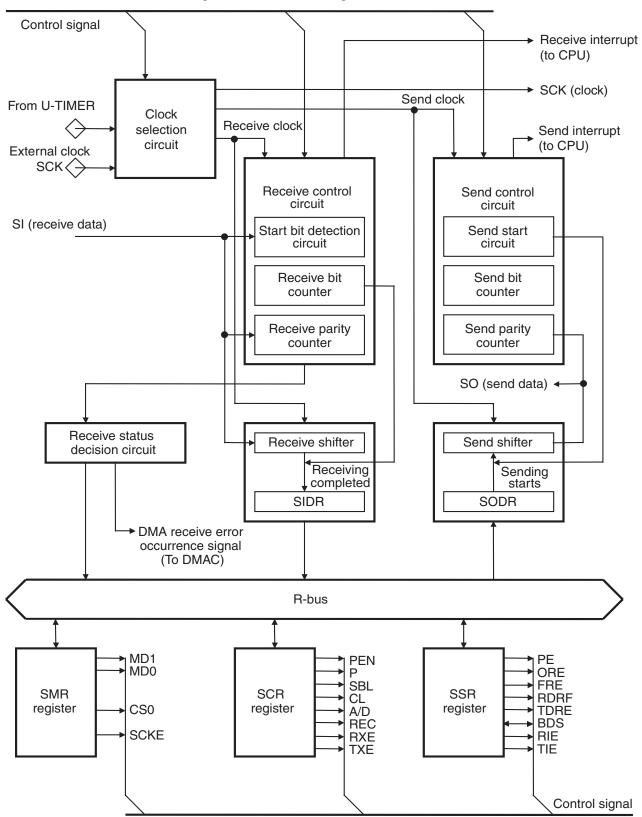

| 13.1 |         | iew of the UART                                                    |     |

| 13.2 |         | Registers                                                          |     |

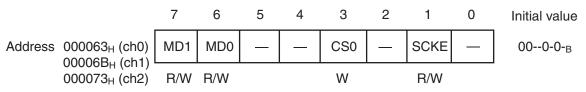

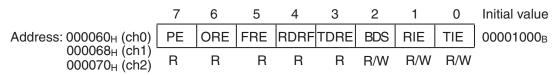

| 13.  |         | rial Mode Register (SMR)                                           |     |

| 13.  |         | rial Control Register (SCR)                                        |     |

| 13.  |         | rial Input Data Register (SIDR)/Serial Output Data Register (SODR) |     |

| 13.  |         | rial Status Register (SSR)                                         |     |

| 13.  |         | CL Register                                                        |     |

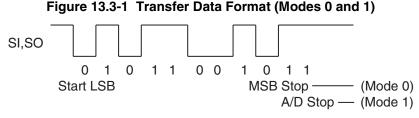

| 13.3 |         | Operation                                                          |     |

| 13.3 |         | ynchronous (Start-stop Synchronization) Mode                       |     |

|      |         | · · · · · · · · · · · · · · · · · · ·                              |     |

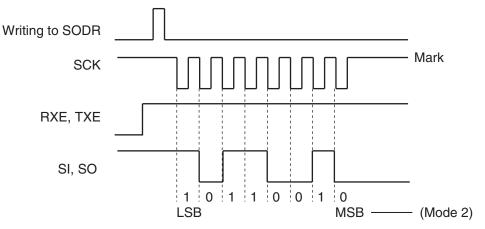

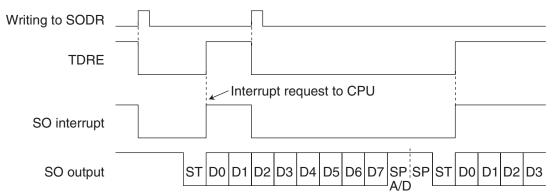

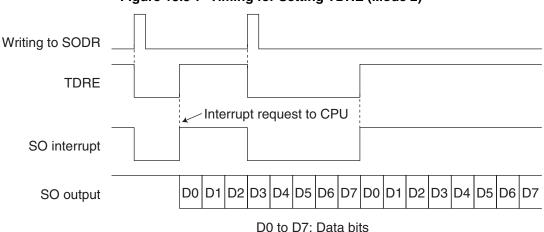

| 13.3  | 2 CLK Synchronous Mode                                      | 377 |

|-------|-------------------------------------------------------------|-----|

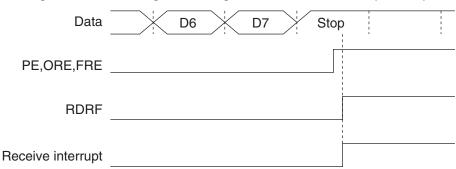

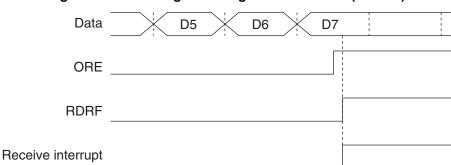

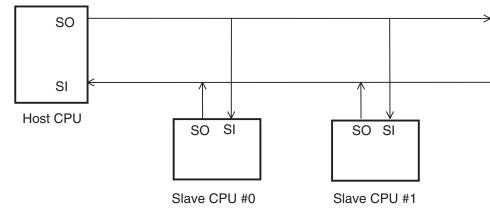

| 13.3  | 3 Occurrence of Interrupts and Timing for Setting Flags     | 379 |

| 13.4  | Example of Using the UART                                   | 382 |

| 13.5  | Example of Setting U-TIMER Baud Rates and Reload Values     |     |

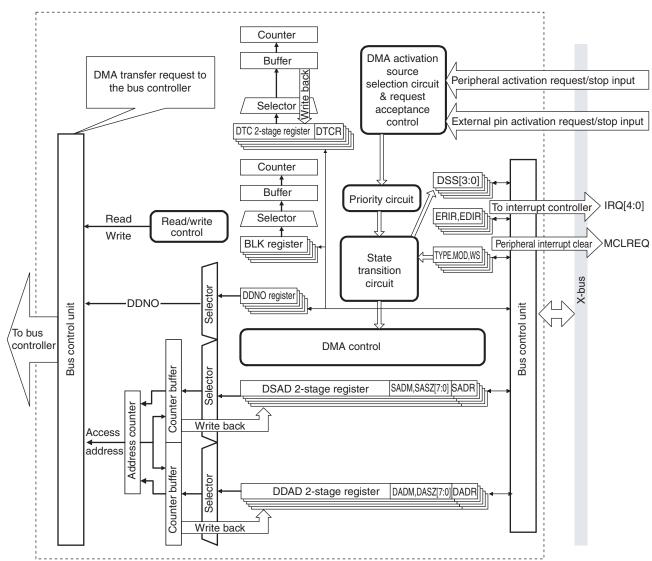

| СНАРТ | ER 14 DMA CONTROLLER (DMAC)                                 | 385 |

| 14.1  | Overview of the DMA Controller (DMAC)                       |     |

| 14.2  | DMA Controller (DMAC) Registers                             |     |

| 14.2  | 1 Control/Status Registers A (DMACA0 to 4)                  | 390 |

| 14.2  | 2 Control/Status Registers B (DMACB0 to 4)                  | 395 |

| 14.2  | 5 5 (                                                       |     |

| 14.2  | 4 DMAC All-Channel Control Register (DMACR)                 |     |

| 14.2  |                                                             |     |

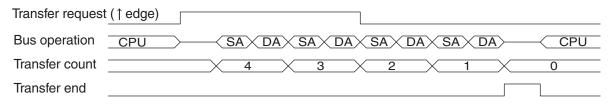

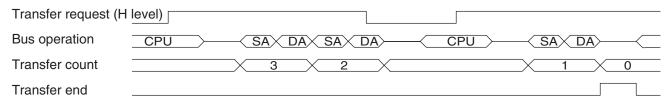

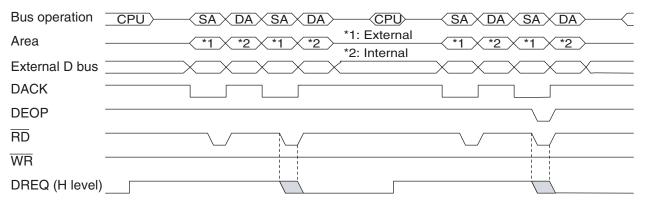

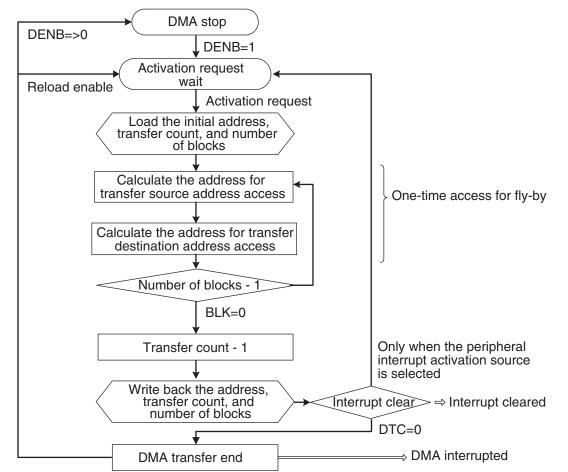

| 14.3  | DMA Controller (DMAC) Operation                             | 407 |

| 14.3  | 1 Setting a Transfer Request                                | 410 |

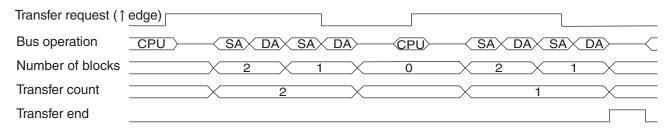

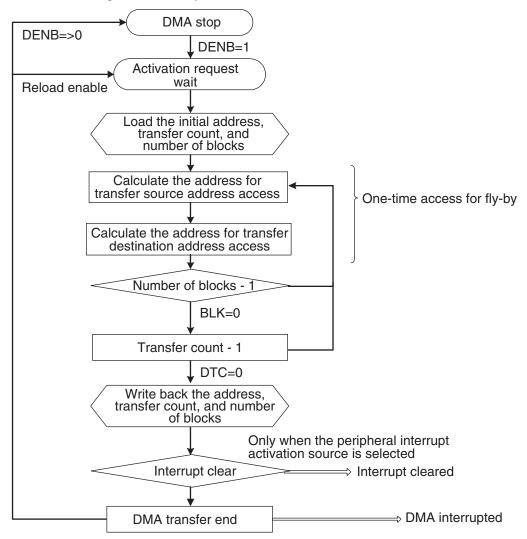

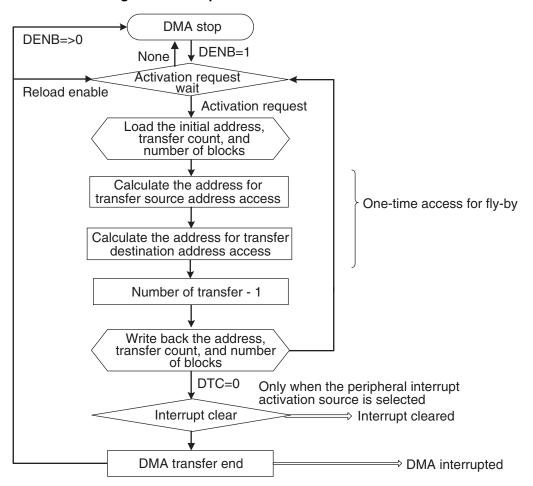

| 14.3  | 2 Transfer Sequence                                         | 411 |

| 14.3  | 3 General Aspects of DMA Transfer                           | 415 |

| 14.3  | 4 Addressing Mode                                           | 417 |

| 14.3  | 5 Data Types                                                | 418 |

| 14.3  | 6 Transfer Count Control                                    | 419 |

| 14.3  | 7 CPU Control                                               | 420 |

| 14.3  |                                                             |     |

| 14.3  | · · · · · · · · · · · · · · · · · · ·                       |     |

| 14.3  | •                                                           |     |

|       | 11 Channel Selection and Control                            |     |

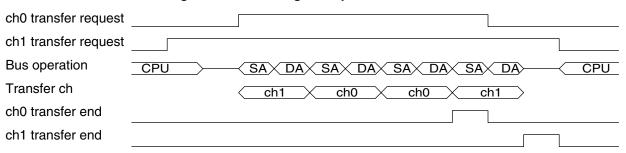

|       | 12 Supplement on External Pin and Internal Operation Timing |     |

| 14.4  | Operation Flowcharts                                        |     |

| 14.5  | Data Bus                                                    |     |

| 14.6  | DMA External Interface                                      |     |

| 14.6  | · · · · · · · · · · · · · · · · · · ·                       |     |

| 14.6  | 2 FR30 Compatible Mode of DACK                              | 441 |

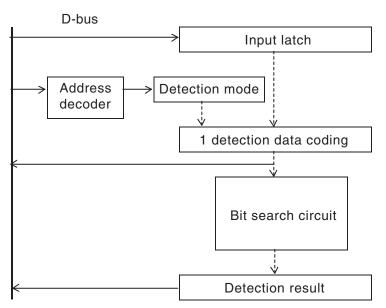

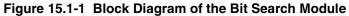

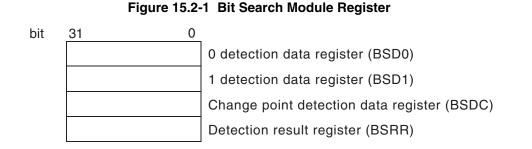

| CHAPT | ER 15 BIT SEARCH MODULE                                     | 443 |

| 15.1  | Overview of the Bit Search Module                           |     |

| 15.2  | Bit Search Module Registers                                 | 445 |

| 15.3  | Bit Search Module Operation                                 | 447 |

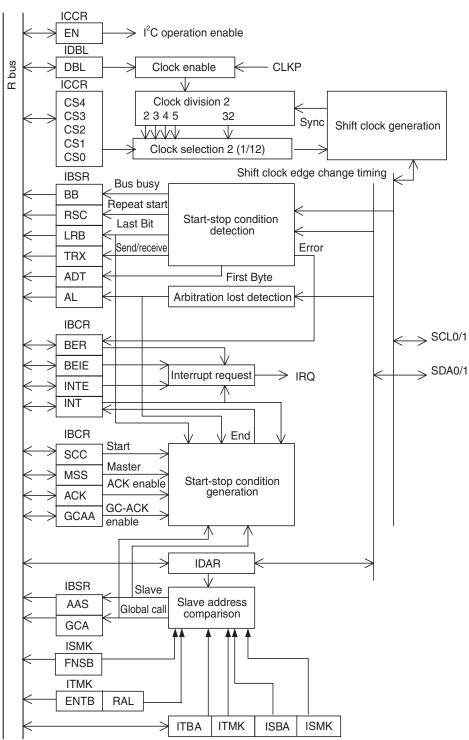

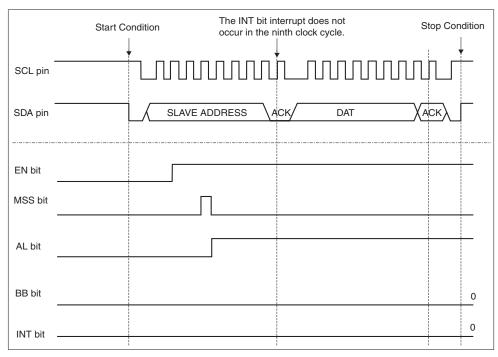

| СНАРТ | ER 16 I <sup>2</sup> C INTERFACE                            | 449 |

| 16.1  | Overview of the I <sup>2</sup> C Interface                  | 450 |

| 16.2  | I <sup>2</sup> C Interface Registers                        |     |

| 16.3  | Block Diagram of I <sup>2</sup> C Interface                 |     |

| 16.4  | Detailed on Registers of the I <sup>2</sup> C Interface     | 454 |

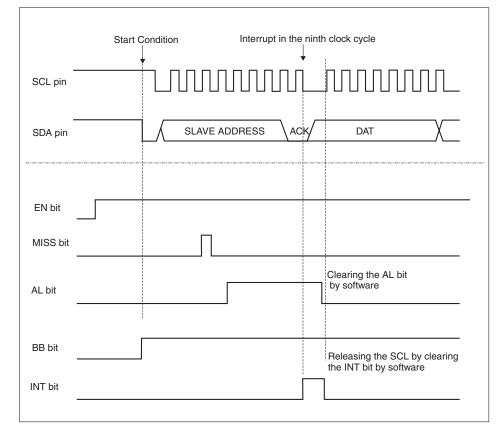

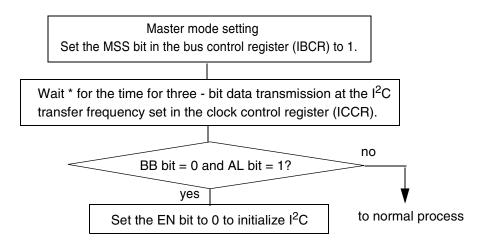

| 16.5  | I <sup>2</sup> C Interface Operation                        | 469 |

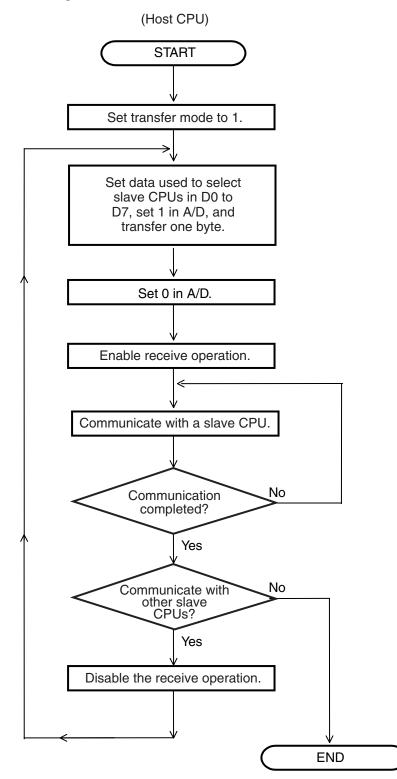

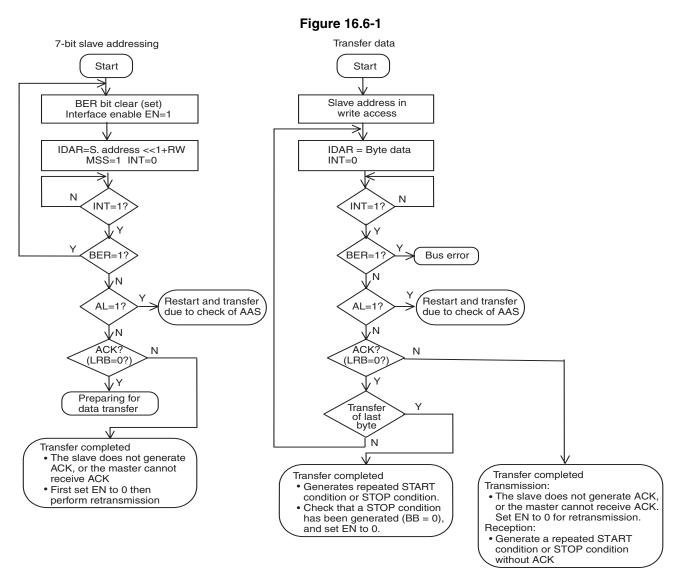

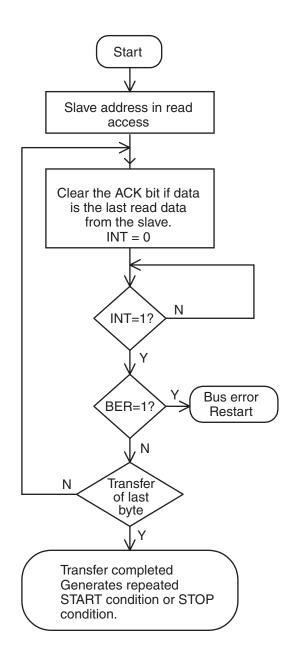

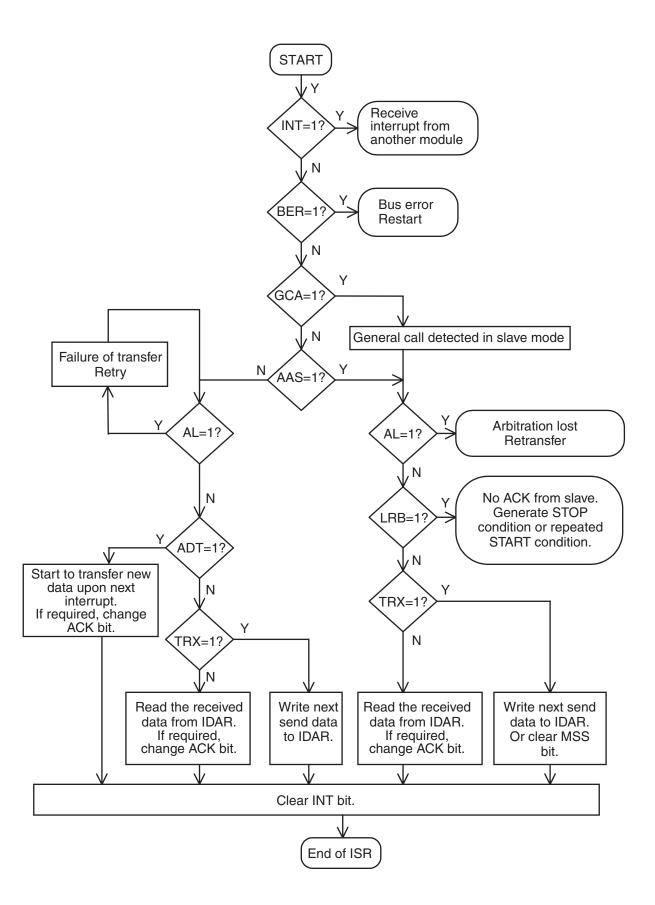

| 16.6  | Operation Flowcharts                                        | 474 |

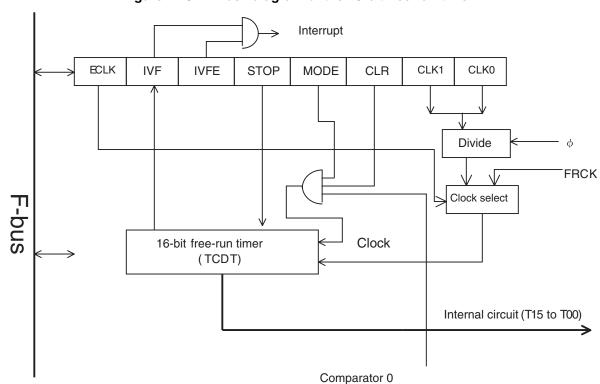

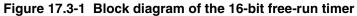

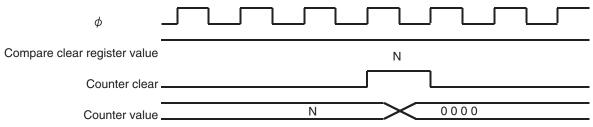

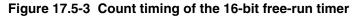

| СНАРТ | ER 17 16-bit Free-run Timer                                 | 477 |

| 17.1  | Overview of 16-bit Free-run Timer                                 | 478             |

|-------|-------------------------------------------------------------------|-----------------|

| 17.2  | Registers of the 16-bit Free-run Timer                            | 479             |

| 17.3  | Block Diagram of the 16-bit Free-run Timer                        | 480             |

| 17.4  | Details on Registers of the 16-bit Free-run Timer                 | 481             |

| 17.5  | Operation of the 16-bit Free-run Timer                            | 485             |

| 17.6  | Precautions on Using the 16-bit Free-run Timer                    | 487             |

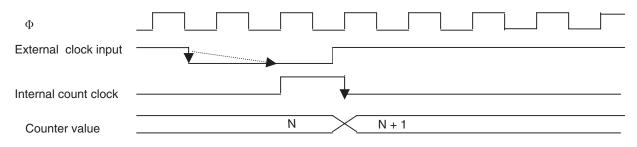

| СНАРТ | ER 18 Input Capture                                               | 489             |

| 18.1  | Overview of Input Capture                                         | 490             |

| 18.2  | Input Capture Registers                                           | 491             |

| 18.3  | Block Diagram of Input Capture                                    | 492             |

| 18.4  | Details on Registers of Input Capture                             | 493             |

| 18.5  | Operation of 16-bit Input Capture                                 | 495             |

| СНАРТ | ER 19 Program Loader Mode (Supported only by the MB91302A         | (IPL integrated |

|       | model))                                                           | 497             |

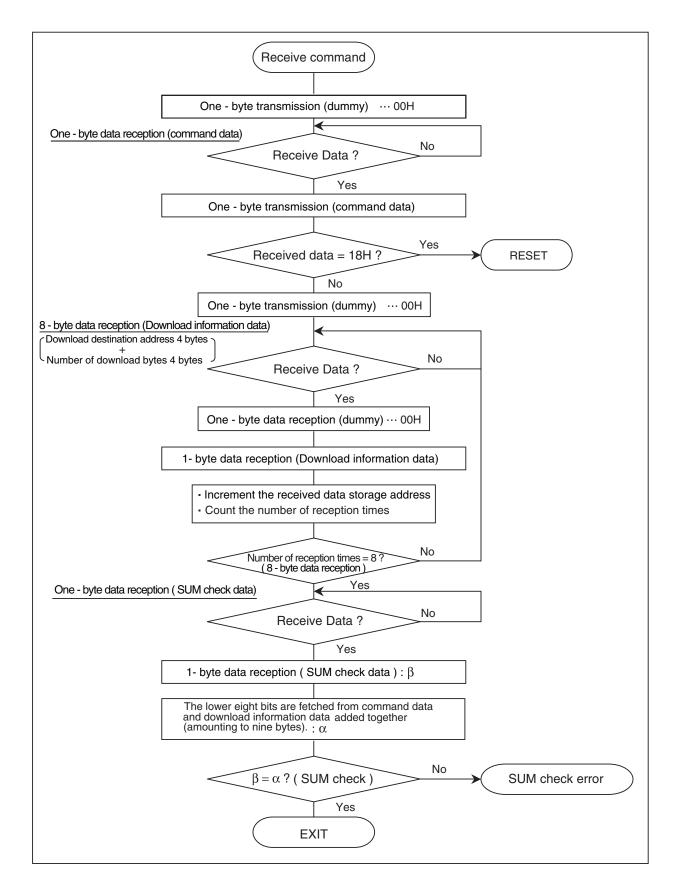

| 19.1  | Overview of the Program Loader Mode                               | 498             |

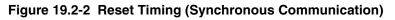

| 19.2  | Setting the Program Loader                                        | 499             |

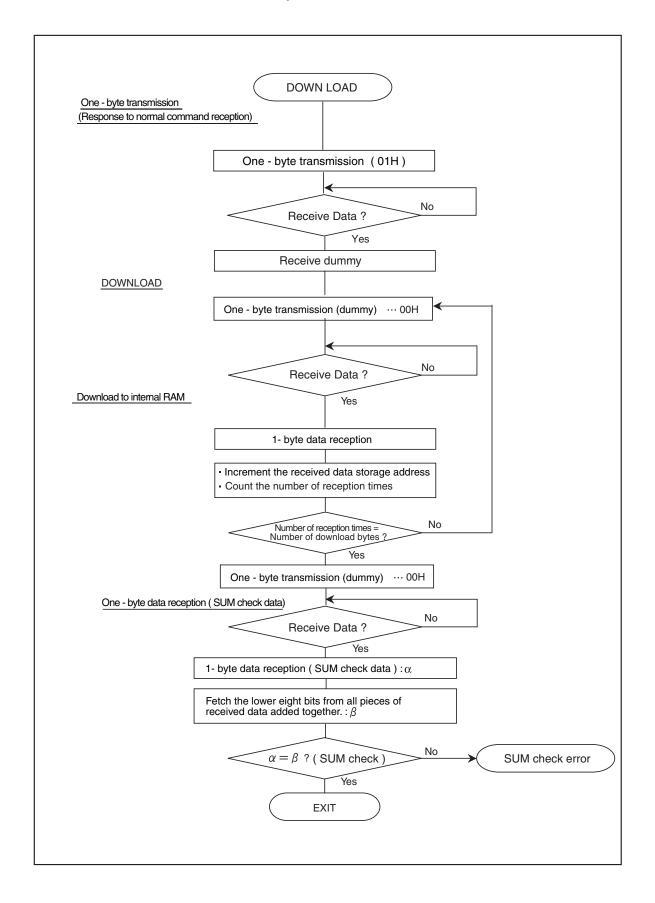

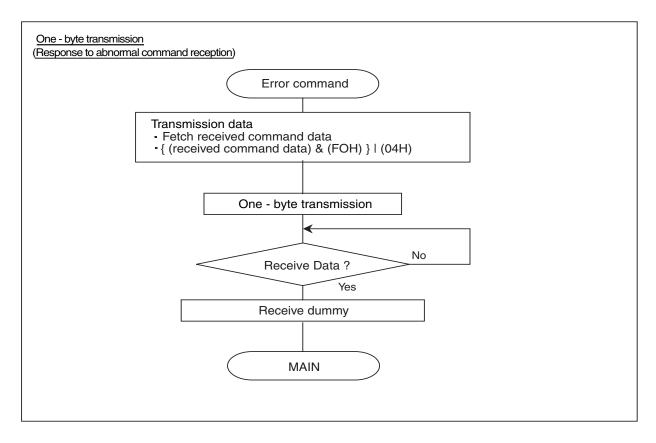

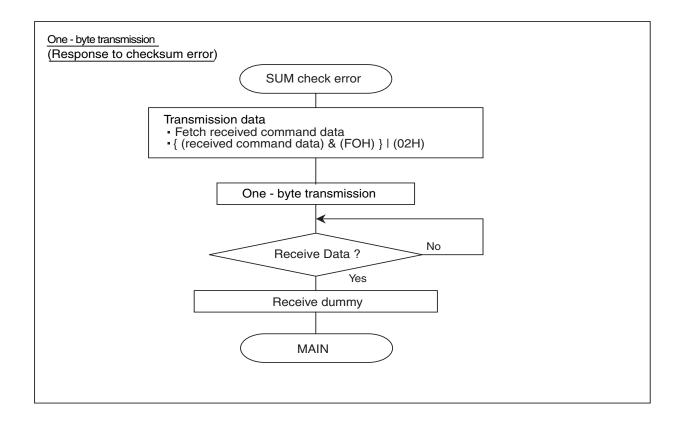

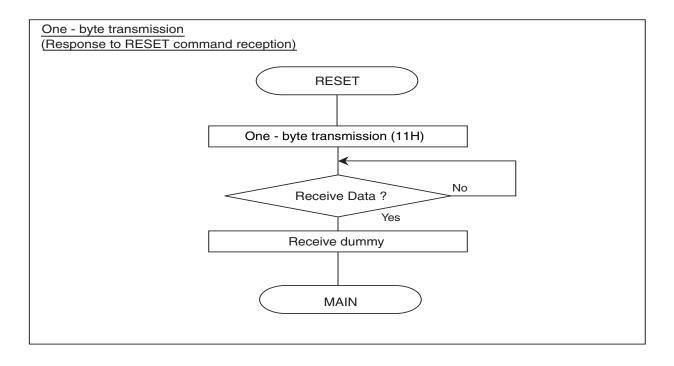

| 19.3  | Operations in the Program Loader Mode                             | 501             |

| 19.4  | Example of Using the Program Loader Mode to Write to Flash Memory | 512             |

| СНАРТ | ER 20 Real - time OS Embedded MB91302A - 010 User's Guide         | 515             |

| 20.1  | Introduction                                                      | 516             |

| 20.2  | Memory Map                                                        | 517             |

| 20.3  | Specifications for REALOS/FR Embedded in MB91302A-010             | 518             |

| 20.4  | Section Allocation                                                | 520             |

| 20.5  | Startup Routine                                                   | 521             |

| 20.6  | Initial Settings for SOFTUNE Workbench and REALOS/FR              | 522             |

| 20.7  | Mode Pins, Mode Vectors, and Reset Vectors                        | 530             |

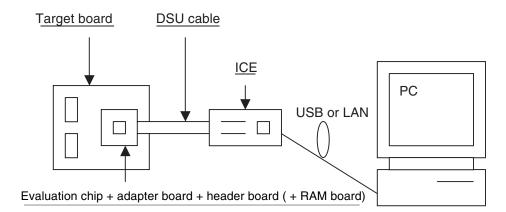

| 20.8  | Chip Evaluation System                                            | 533             |

| APPEN | DIX                                                               | 535             |

| APPE  | NDIX A I/O MAP                                                    | 536             |

| APPE  | NDIX B INTERRUPT VECTOR                                           | 548             |

| APPE  | NDIX C PIN STATE IN EACH CPU STATE                                | 552             |

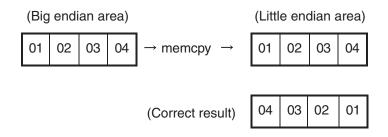

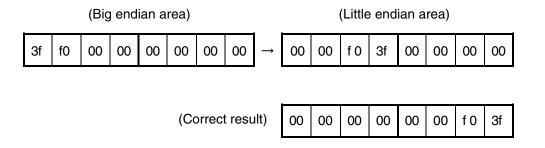

| APPE  | NDIX D NOTES ON USING A LITTLE ENDIAN AREA                        | 566             |

| D.1   | C Compiler (fcc911)                                               | 567             |

| D.2   | Assembler (fasm911)                                               | 570             |

| D.3   | Linker (flnk911)                                                  | 572             |

| D.4   | Debugger (sim911, eml911, mon911)                                 |                 |

| APPE  | NDIX E INSTRUCTION LISTS                                          |                 |

| E.1   | How to Read the Instruction Lists                                 | 575             |

| E.2   | FR Family Instruction Lists                                       | 579             |

# This chapter provides basic information required to understand the MB91301 series, and covers features, a block diagram, and functions.

- 1.1 "Features of the MB91301 Series"

- 1.2 "Block Diagram"

- 1.3 "External Dimensions"

- 1.4 "Pin Layout"

- 1.5 "Pin No. Table"

- 1.6 "List of Pin Functions"

- 1.7 "Input-output Circuit Forms"

## 1.1 Features of the MB91301 Series

The MB91301 series is a standard single-chip microcontroller that has a 32-bit highperformance RISC CPU as well as built-in I/O resources and bus control mechanisms for embedded controller requiring high-performance and high-speed CPU processing. Although the MB91301 series basically uses external bus access to support a vast address space accessed by a 32-bit CPU, it has a 4 KB instruction cache memory and 4 KB RAM to increase the speed at which the CPU executes instructions.

This model is an FR60 series model that is based on the FR30/40-family of CPUs. It has enhanced bus access and is optimized for high-speed use.

The MB91301 series is most suitable for embedded applications, such as digital video cameras, navigation systems, and DVD players, that require a high level of CPU processing power.

#### ■ Features of the MB91301 Series

The MB91301 series has the line-up of series embedde the each of program in built-in ROM.

| ROM variation<br>Products | Real time OS internal version | IPL (internal<br>program loader)<br>internal version | User ROM<br>version | No ROM version |

|---------------------------|-------------------------------|------------------------------------------------------|---------------------|----------------|

| MB91302A                  | 0                             | 0                                                    | 0                   | 0              |

| MB91301                   | Х                             | Х                                                    | Х                   | 0              |

#### FR CPU

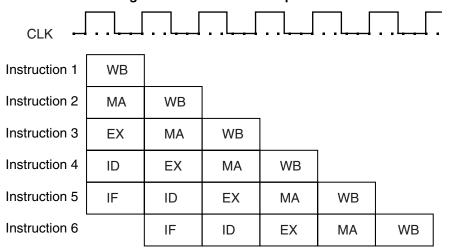

- 32-bit RISC, load/store architecture, five pipelines

- Operating frequency of 68 MHz (Internal maximum value), 68 MHz (External maximum value) [PLL used, original oscillation at 17 MHz]

- 32-bit general-purpose register x 16

- 16-bit fixed-length instructions (basic instructions), one instruction per cycle

- Memory-to-memory transfer, bit processing, instructions, including barrel shift, etc.; instructions appropriate for embedded applications

- Function entry and exit instructions, multi load/store instructions--instructions compatible with high-level languages

- Instructions for entry/exit functions, multiple load/store instructions for the register contents, instructions for high-level languages.

- · Register interlock function to facilitate assembly-language coding

- Branch instruction with a delay slot allowing a decrease in overhead for branch processing

- · Built-in multiplier/instruction-level support

- Signed 32-bit multiplication: 5 cycles

- Signed 16-bit multiplication: 3 cycles

- Interrupts (saving of PC and PS): 6 cycles, 16 priority levels

#### Bus Interface

- Maximum operating frequency of 68 MHz (at using SRAM)

- 24-bit address can be fully output (16 MB space)

- 8-, 16- and 32-bit data I/O

- Prefetch buffer installed

- Unused data and address pins can be used as general-purpose I/O ports.

- Totally independent 8-area chip select output that can be defined at a minimum of 64 KB

- Support of interfaces for various memory modules

- Asynchronous SRAM, asynchronous ROM/FLASH

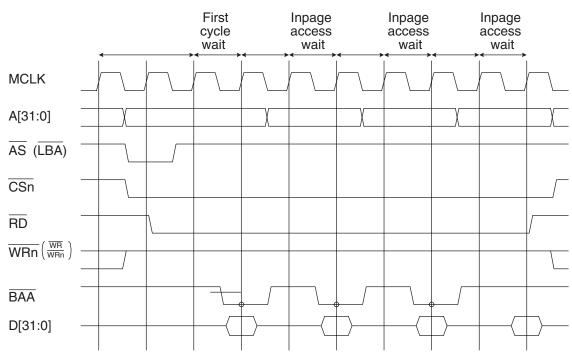

- Page-mode ROM/FLASHROM (a page-size of 1, 2, 4, or 8 can be selected)

- Burst-mode ROM/FLASH (MBM29BL160D/161D/162D etc.)

- SDRAM (or FCRAM type, CAS Latency1 to 8, 2/4 bank product)

- Address/data multiplexed bus (8 bit/16 bit width only)

- Basic bus cycle: 2 cycles

- Automatic wait cycle generator (Max 15 cycles) that can be programmed for each area and can insert waits

- External wait cycles due to RDY input

- Endian setting of byte ordering (big/little) CS0 are, however, is only big endian

- Write disable setting (read only data)

- Enable/disable set of captureing to the built-in cache

- Enable/disable set of prefetch function

- Supports fly-by DMA transfer that enables independent I/O wait control

- External bus arbitration using BRQ and BGRNT is enabled

#### Built-in Memory

- DATA RAM: 4KB

- ROM: 4FB (MB91302A)

Built-in 8KB DATA RAM and 8 KB DATA/Instruction RAM in MB91V301

Built-in 8 KB DATA RAM, 8 KB DATA/instruction RAM and 8 KB emulation RAM in MB91V301A

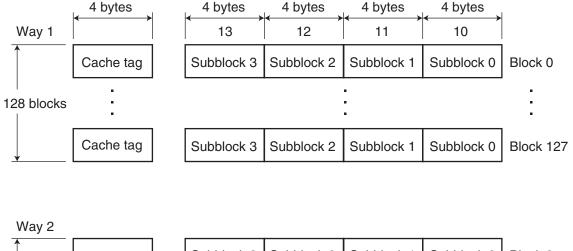

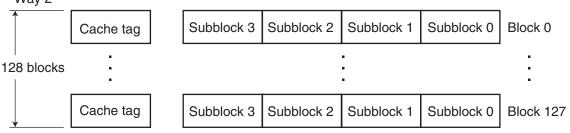

#### Instruction Cache

- Capacity of 4 KB

- 2 way set associative

- 128 block/way, 4 entry (4 words)/block

- Lock function allows specific program codes to stay resident in cache

- · Instruction RAM function: A part of the instruction cache not in use can be used as RAM

#### DMAC (DMA Controller)

5 channels (2 channels for external to request)

- 3 transfer sources (external pins, internal peripherals, software)

- Internal peripheral can be selected at each channel as the transfer factor

- Addressing mode with 32-bit full address specifications (increase, decrease, fixed)

- Transfer modes (demand transfer, burst transfer, step transfer, block transfer)

- Fly-by transfer supported (three channels between external I/O and external memory)

- Transfer data size that can be selected from 8, 16, and 32 bits

#### Bit Search Module

• Searches for the position of the first bit varying between 1 and 0 in the MSB of a word

#### Reload Timer (including One Channel for REALOS)

- 16-bit timer; 3 channels

- Internal clock: 2-clock cycle resolution, selectable from 2, 8 or 32 dividen frequency

#### UART

- UART full-duplex double buffer

- Independent 3 channels

- Data length: 7 to 9 bits (no parity), 8 to 8 bits (parity)

- Either asynchronous (start-stop synchronization) or CLK synchronous communication can be selected.

- Multi processor mode

- Built-in 16-bit timer (U-TIMER) as boud rate generater: generatin arbitrary baud rates

- An external clock can be used as the transfer clock.

- Error detection functions (parity, frame, overrun)

#### Interrupt Controller

- Total of 9 external interrupts (one unmaskable pin (NMI) and eight regular interrupt pins (INT7 to INT0))

- Internal interrupt source: UART, DMAC, A/D, UTIMER, delay interrupt, I<sup>2</sup>C, free-running timer and ICU

- The I<sup>2</sup>C, free running timer, and ICU are sources unique to the MB91302A and MB91V301A.

- Priority level can be defined as programmable (16 levels) except for the unmaskable pin

#### ■ A/D Converter (sequential conversion type)

- 10-bit resolution, 4 channels

- Sequential comparison and conversion type: peripheral clock (CLKP) 140 clock cycle conversion time (about 4.1  $\mu$ s/ch at 34MHz operating)

- Built-in sample and hold circuit

- Conversion modes (single-shot conversion mode, scan conversion mode, and repeat conversion mode)

- · Causes of startup (select from software, external triggers, and internal timer)

- I<sup>2</sup>C Interface

- Master/slave transmission and reception

- Clock synchronization function

- Arbitration function

- The I<sup>2</sup>C bus interface is only for MB91302A, MB91301A.

#### Free Run Timer

- 16-bit 1channel

- Input capture 4 channels

- Free run timer is only for MB9130A an MB91V301A.

#### Other Interval Timers

- 16-bit timer: 3 channels (U-TIMER)

- PPG timer: 4channels

- Watchdog timer; 1 channel

#### Other Features

- Has a built-in oscillation circuit as a clock source for which PLL multiplication can be selected.

- INIT is provided as a reset pin.

- · Additionally, a watchdog timer reset and software resets are provided.

- Stop mode and sleep mode supported as low-power modes

- Gear function

Allows arbitrary different operating clock frequencies to be set for the CPU and peripherals. The gear clock factor can be selected from among 16 options: 1/1, 1/2, 1/3, 1/4, 1/5, 1/6, 1/7, 1/8,...., 1/16. Note that the maximum operating frequency of peripherals is 34 MHz.

- Built-in time base timer

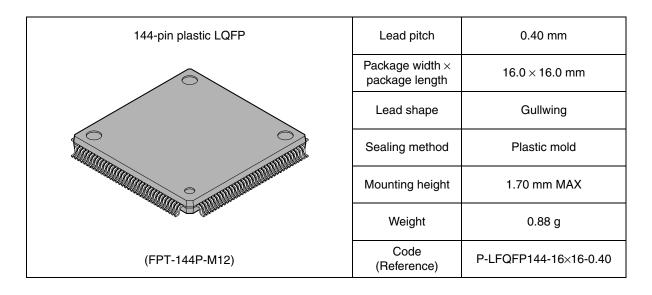

- Packages

- MB91301/302A (FPT-144P-M12)

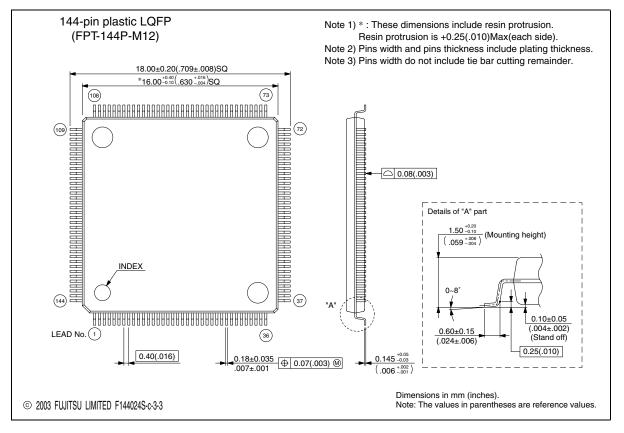

- MB91V301/V301A (PGA-179C-A03)

- CMOS technology

- 0.25 μm

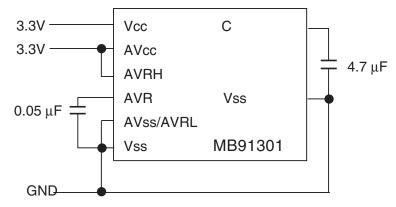

- Power voltages

- Power supply (analog power supply): 3.3 V ± 0.3 V (at using internal regulator)

- On chip Device Support Unit (DSU4) is installed in MB91V301/V301A.

#### Product Line-up

|         | MB91301                                         | MB91V301                                                                                                                                                                                                   | MB91302A                                    | MB91V301A                                                   |

|---------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------|

| Туре    | External ROM version<br>(for volume production) | Evaluation version<br>(For evaluation and de-<br>velopment)                                                                                                                                                | Mask ROM product<br>(for volume production) | Evaluation version<br>(For evaluation and de-<br>velopment) |

| RAM     | 4 KB<br>(only for data)                         | 16 KB<br>(data 8 KB+8 KB)                                                                                                                                                                                  | 4 KB<br>(only for data)                     | 16 KB<br>(data 8 KB+8 KB)                                   |

| ROM     | -                                               | - 4 KB<br>ROM has non-ROM model, the<br>optimal real time OS internal<br>model* <sup>1</sup> , and the IPL (Internal<br>Program Loader) internal mod-<br>el* <sup>2</sup> by adding the user ROM<br>model. |                                             | 8 KB (RAM)                                                  |

| DSU     | -                                               | DSU4                                                                                                                                                                                                       | -                                           | DSU4                                                        |

| Package | LQFP-144<br>(0.4 mm pitch)                      | PGA-179                                                                                                                                                                                                    | LQFP-144<br>(0.4 mm pitch)                  | PGA-179                                                     |

| Other   | Currently in production                         | Currently available                                                                                                                                                                                        | Currently in production                     | Currently available                                         |

\*1: The Fujitsu product of real time OS REALOS/FR by conforming to the μITORN 3.0 is stored and optimized with the MB91302A. For details of built-in service call type and the specification of user task, see "CHAPTER 20 Real - time OS Embedded MB91302A - 010 User's Guide" and following manual;

- FR FAMILY SOFTUNE REALOS/ FR USER'S GUIDE

- FR FAMILY SOFTUNE REALOS/ FR KERNEL MANUAL

- + FR-V/ FR FAMILY CONFORMING TO  $\mu ITRON4.0$  SPECIFICATIONS SOFTUNE REALOS CONFIGURATOR MANUAL

- FR-V/ FR/ F<sup>2</sup>MC FAMILY SOFTUNE REALOS ANALYZER MANUAL

- 2: The ROM stores the IPL (Internal Program Loader). Loading various programs can be executed from the external system by the internal UART/SIO. Using this function, for example, writing on board to the Flash memory connected to the external can be executed.

## 1.2 Block Diagram

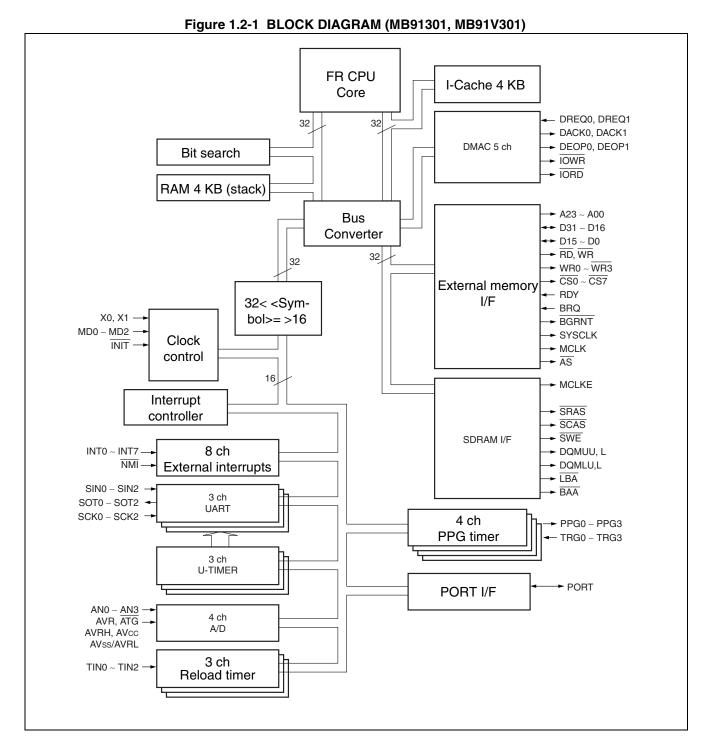

#### Figure 1.2-1 "Block Diagram" is a block diagram of the MB91301 series.

#### Block Diagram

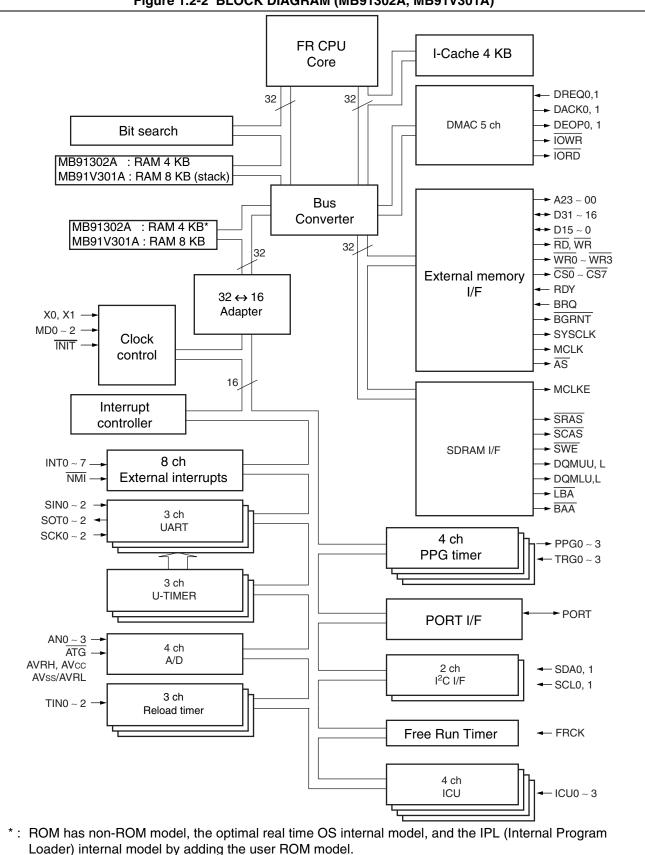

Figure 1.2-2 BLOCK DIAGRAM (MB91302A, MB91V301A)

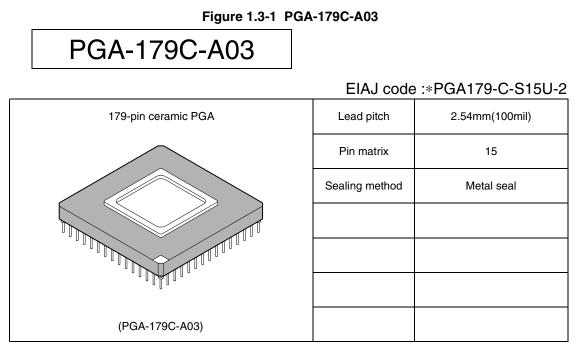

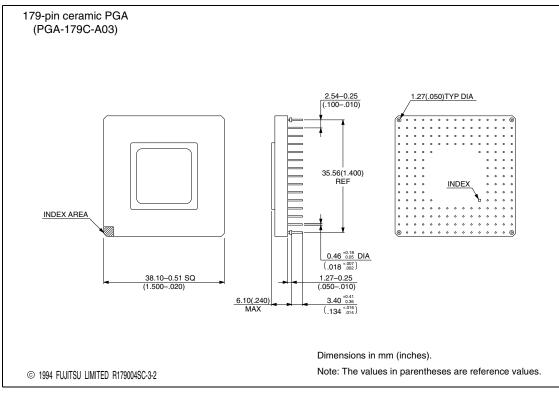

## **1.3 External Dimensions**

#### The MB91301 series is available in one type of package.

#### Dimensions

#### Figure 1.3-2 FPT-144P-M12

# FPT-144P-M12

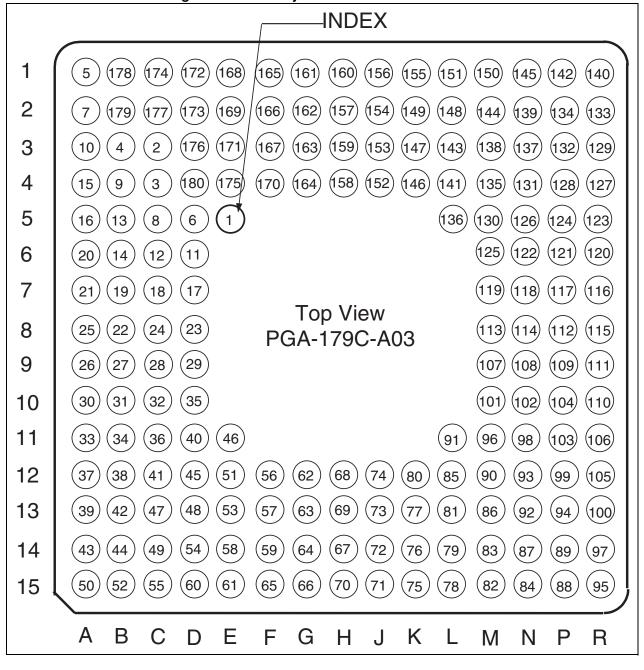

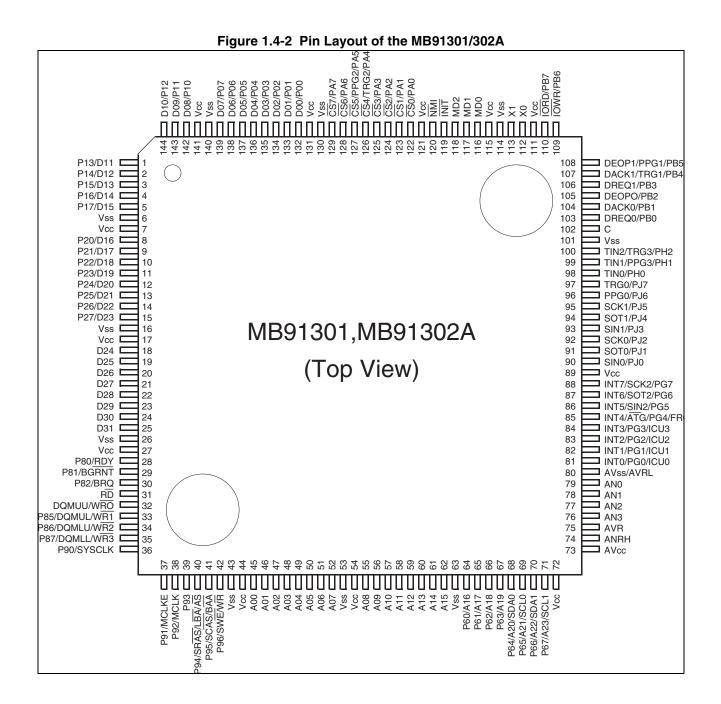

### 1.4 Pin Layout

#### This section shows the pin layout of the MB91301 series.

#### ■ Pin Layout of the MB91V301/V301A

Figure 1.4-1 "Pin Layout of the MB91V301/V301A" is a diagram of the pin layout of the MB91V301/V301A.

Figure 1.4-1 Pin Layout of the MB91V301/V301A

#### ■ Pin Layout of the MB91301/302A

## 1.5 Pin No. Table

#### The pin No. table of the MB91V301/V301A is shown.

#### Pin No. Table

#### Table 1.5-1 MB91V301/V301A Pin No. Table (Package: PGA-179C-A03)

| No. | PIN | Pin Name        | No. | PIN | Pin Name         | No. | PIN | Pin Name                            |

|-----|-----|-----------------|-----|-----|------------------|-----|-----|-------------------------------------|

| 1   | E5  | N.C.            | 31  | B10 | V <sub>SS</sub>  | 61  | E15 | A07                                 |

| 2   | C3  | P13/D11         | 32  | C10 | V <sub>CC</sub>  | 62  | G12 | V <sub>SS</sub>                     |

| 3   | C4  | V <sub>SS</sub> | 33  | A11 | P80/RDY          | 63  | G13 | V <sub>CC</sub>                     |

| 4   | B3  | V <sub>CC</sub> | 34  | B11 | P81/BGRNT        | 64  | G14 | A08                                 |

| 5   | A1  | P14/D12         | 35  | D10 | P82/BRQ          | 65  | F15 | A09                                 |

| 6   | D5  | P15/D13         | 36  | C11 | RD               | 66  | G15 | A10                                 |

| 7   | A2  | P16/D14         | 37  | A12 | DQMUU/WR0        | 67  | H14 | A11                                 |

| 8   | C5  | P17/D15         | 38  | B12 | P85/DQMUL/WR1    | 68  | H12 | A12                                 |

| 9   | B4  | V <sub>SS</sub> | 39  | A13 | P86/DQMLU/WR2    | 69  | H13 | A13                                 |

| 10  | A3  | V <sub>CC</sub> | 40  | D11 | P87/DQMLL/WR3    | 70  | H15 | A14                                 |

| 11  | D6  | P20/D16         | 41  | C12 | V <sub>SS</sub>  | 71  | J15 | A15                                 |

| 12  | C6  | P21/D17         | 42  | B13 | V <sub>CC</sub>  | 72  | J14 | V <sub>SS</sub>                     |

| 13  | B5  | P22/D18         | 43  | A14 | P90/SYSCLK       | 73  | J13 | V <sub>CC</sub>                     |

| 14  | B6  | P23/D19         | 44  | B14 | P91/MCLKE        | 74  | J12 | P60/A16                             |

| 15  | A4  | P24/D20         | 45  | D12 | P92/MCLK         | 75  | K15 | P61/A17                             |

| 16  | A5  | P25/D21         | 46  | E11 | P93              | 76  | K14 | P62/A18                             |

| 17  | D7  | P26/D22         | 47  | C13 | V <sub>SS</sub>  | 77  | K13 | P63/A19                             |

| 18  | C7  | P27/D23         | 48  | D13 | V <sub>CC</sub>  | 78  | L15 | SDA0/P64/A20<br>SDA0;MB91V301A only |

| 19  | B7  | V <sub>SS</sub> | 49  | C14 | P94/SRAS/LABA/AS | 79  | L14 | SCL0/P65/A21<br>SCL0;MB91V301A only |

| 20  | A6  | V <sub>CC</sub> | 50  | A15 | P95/SCAS/BAA     | 80  | K12 | SDA1/P66/A22<br>SDA1;MB91V301A only |

| 21  | A7  | D24             | 51  | E12 | P96/SWE/WR       | 81  | L13 | SCL1/P67/A23<br>SCL1;MB91V301A only |

| 22  | B8  | D25             | 52  | B15 | V <sub>SS</sub>  | 82  | M15 | V <sub>CC</sub>                     |

| 23  | D8  | D26             | 53  | E13 | V <sub>CC</sub>  | 83  | M14 | V <sub>CC</sub>                     |

| 24  | C8  | D27             | 54  | D14 | A00              | 84  | N15 | EWR3                                |

| 25  | A8  | V <sub>SS</sub> | 55  | C15 | A01              | 85  | L12 | EWR2                                |

| 26  | A9  | V <sub>CC</sub> | 56  | F12 | A02              | 86  | M13 | EWR1                                |

| 27  | B9  | D28             | 57  | F13 | A03              | 87  | N14 | EWR0                                |

| 28  | C9  | D29             | 58  | E14 | A04              | 88  | P15 | ECS                                 |

| 29  | D9  | D30             | 59  | F14 | A05              | 89  | P14 | EMRAM                               |

| 30  | A10 | D31             | 60  | D15 | A06              | 90  | M12 | ICD3                                |

| No. | PIN | Pin Name                                 | No. | PIN | Pin Name        | No. | PIN | Pin Name        |

|-----|-----|------------------------------------------|-----|-----|-----------------|-----|-----|-----------------|

| 91  | L11 | ICD2                                     | 121 | P6  | SOT0/PJ1        | 151 | L1  | V <sub>CC</sub> |

| 92  | N13 | ICD1                                     | 122 | N6  | SCK0/PJ2        | 152 | J4  | INIT            |

| 93  | N12 | ICD0                                     | 123 | R5  | SIN1/PJ3        | 153 | J3  | NMI             |

| 94  | P13 | V <sub>SS</sub>                          | 124 | P5  | SOT1/PJ4        | 154 | J2  | V <sub>SS</sub> |

| 95  | R15 | V <sub>CC</sub>                          | 125 | M6  | SCK1/PJ5        | 155 | K1  | V <sub>CC</sub> |

| 96  | M11 | BREAK                                    | 126 | N5  | PPG0/PJ6        | 156 | J1  | CS0/PA0         |

| 97  | R14 | ICLK                                     | 127 | R4  | TRG0/PJ7        | 157 | H2  | CS1/PA1         |

| 98  | N11 | ICS2                                     | 128 | P4  | TIN0/PH0        | 158 | H4  | CS2/PA2         |

| 99  | P12 | ICS1                                     | 129 | R3  | TIN1/PPG3/PH1   | 159 | H3  | CS3/PA3         |

| 100 | R13 | ICS0                                     | 130 | M5  | TIN2/TRG3/PH2   | 160 | H1  | CS4/TRG2/PA4    |

| 101 | M10 | TRST                                     | 131 | N4  | V <sub>SS</sub> | 161 | G1  | CS5/PPG2/PA5    |

| 102 | N10 | С                                        | 132 | P3  | С               | 162 | G2  | CS6/PA6         |

| 103 | P11 | AV <sub>CC</sub>                         | 133 | R2  | DREQ0/PB0       | 163 | G3  | CS7/PA7         |

| 104 | P10 | AVRH                                     | 134 | P2  | DACK0/PB1       | 164 | G4  | V <sub>SS</sub> |

| 105 | R12 | AVR                                      | 135 | M4  | DEOP0/PB2       | 165 | F1  | V <sub>CC</sub> |

| 106 | R11 | AN3                                      | 136 | L5  | DREQ1/PB3       | 166 | F2  | D00/P00         |

| 107 | M9  | AN2                                      | 137 | N3  | DACK1/TRG1/PB4  | 167 | F3  | D01/P01         |

| 108 | N9  | AN1                                      | 138 | М3  | DEOP1/PPG1/PB5  | 168 | E1  | D02/P02         |

| 109 | P9  | AN0                                      | 139 | N2  | IOWR/PB6        | 169 | E2  | D03/P03         |

| 110 | R10 | AV <sub>SS</sub> /AVRL                   | 140 | R1  | IORD/PB7        | 170 | F4  | V <sub>SS</sub> |

| 111 | R9  | INT0/PG0/ICU0<br>ICU0;MB91V301A only     | 141 | L4  | V <sub>CC</sub> | 171 | E3  | V <sub>CC</sub> |

| 112 | P8  | INT1/PG1/ICU1<br>ICU1;MB91V301A only     | 142 | P1  | V <sub>SS</sub> | 172 | D1  | D04/P04         |

| 113 | M8  | INT2/PG2/ICU2<br>ICU2;MB91V301A only     | 143 | L3  | X0              | 173 | D2  | D05/P05         |

| 114 | N8  | INT3/PG3/ICU3<br>ICU3;MB91V301A only     | 144 | M2  | X1              | 174 | C1  | D06/P06         |

| 115 | R8  | INT4/ATG/PG4/FRCK<br>FRCK;MB91V301A only | 145 | N1  | V <sub>SS</sub> | 175 | E4  | D07/P07         |

| 116 | R7  | INT5/SIN2/PG5                            | 146 | K4  | V <sub>CC</sub> | 176 | D3  | V <sub>SS</sub> |

| 117 | P7  | INT6/SOT2/PG6                            | 147 | K3  | MD0             | 177 | C2  | V <sub>CC</sub> |

| 118 | N7  | INT7/SCK2/PG7                            | 148 | L2  | MD1             | 178 | B1  | D08/P10         |

| 119 | M7  | V <sub>CC</sub>                          | 149 | K2  | MD2             | 179 | B2  | D09/P11         |

| 120 | R6  | SIN0/PJ0                                 | 150 | M1  | V <sub>CC</sub> | 180 | D4  | D10/P12         |

## 1.6 List of Pin Functions

#### This section describes the pin functions of the MB91301 series.

#### Description of Pin Functions

Table 1.6-1 lists the pin of the MB91301 series and their functions.

| Table 1.6-1 | List of | pin function ( | except for | power supp | oly, and GND p | oins) |

|-------------|---------|----------------|------------|------------|----------------|-------|

|-------------|---------|----------------|------------|------------|----------------|-------|

| Pin no.          |                       | Pin name      | I/O circ             | uit type               | Function                                                                                                                                                          |

|------------------|-----------------------|---------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MB91301/<br>302A | MB91V301/<br>V301A    |               | MB91301,<br>MB91V301 | MB91302A,<br>MB91V301A |                                                                                                                                                                   |

| 132 to<br>139    | 166 to<br>169, 172    | D00 to<br>D07 | J                    |                        | External data bus bits 0 to 7. It is available in the external bus mode.                                                                                          |

|                  | to 175                | P00 to<br>P07 |                      |                        | Can be used as ports in 8-bit or 16-bit external bus mode.                                                                                                        |

| 142 to<br>144,   | 178 to<br>180, 2, 5   | D08 to<br>D15 | J                    |                        | External data bus bits 08 to 15.<br>It is available in the external bus mode.                                                                                     |

| 1 to 5           | to 8                  | P10 to<br>P17 |                      |                        | Can be used as ports in 8-bit or 16-bit external bus mode.                                                                                                        |

| 8 to 15          | 11 to 18              | D16 to<br>D23 | J                    |                        | External data bus bits 16 to 23.<br>It is available in the external bus mode.                                                                                     |

|                  |                       | P20 to<br>P27 |                      |                        | Can be used as ports in 8-bit external bus mode.                                                                                                                  |

| 18 to 25         | 21 to 24,<br>27 to 30 | D24 to<br>D31 | С                    |                        | External data bus bits 24 to 31.<br>It is available in the external bus mode.                                                                                     |

| 28               | 33                    | RDY           |                      | J                      | [RDY] External ready input. The pin<br>has this function when external ready<br>input is enabled. Active level is "H".                                            |

|                  |                       | P80           |                      |                        | [P80] General purpose input/output<br>port. The pin has this function when<br>external ready input is disabled.                                                   |

| 29               | 34                    | BGRNT         |                      | J                      | [BGRNT] Acknowledge output for<br>external bus release.<br>Outputs "L" when the external bus is<br>released. The pin has this function<br>when output is enabled. |

|                  |                       | P81           |                      |                        | [P81] General purpose input/output<br>port. The pin has this function when<br>output is disabled for external bus<br>release acknowledge.                         |

| Pin no.          |                    | Pin name      | I/O circ             | uit type               | Function                                                                                                                                                                                                                                |

|------------------|--------------------|---------------|----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MB91301/<br>302A | MB91V301/<br>V301A |               | MB91301,<br>MB91V301 | MB91302A,<br>MB91V301A |                                                                                                                                                                                                                                         |

| 30               | 35                 | BRQ           | J                    |                        | [BRQ] External bus release request<br>input. Input "1" to request release of<br>the external bus. The pin has this<br>function when input is enabled.                                                                                   |

|                  |                    | P82           |                      |                        | [P82] General purpose input/output<br>port. The pin has this function when the<br>external bus release request input is<br>disabled.                                                                                                    |

| 31               | 36                 | RD            | С                    |                        | [RD] External bus read strobe output.<br>This pin is enabled at external bus<br>mode.                                                                                                                                                   |

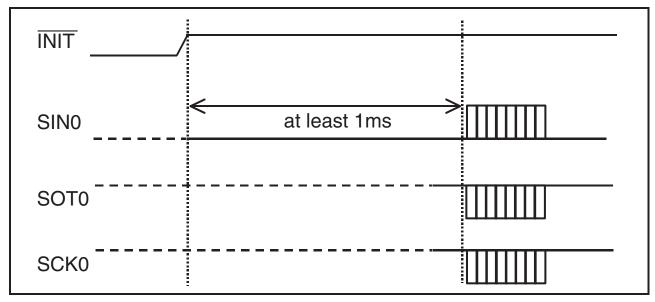

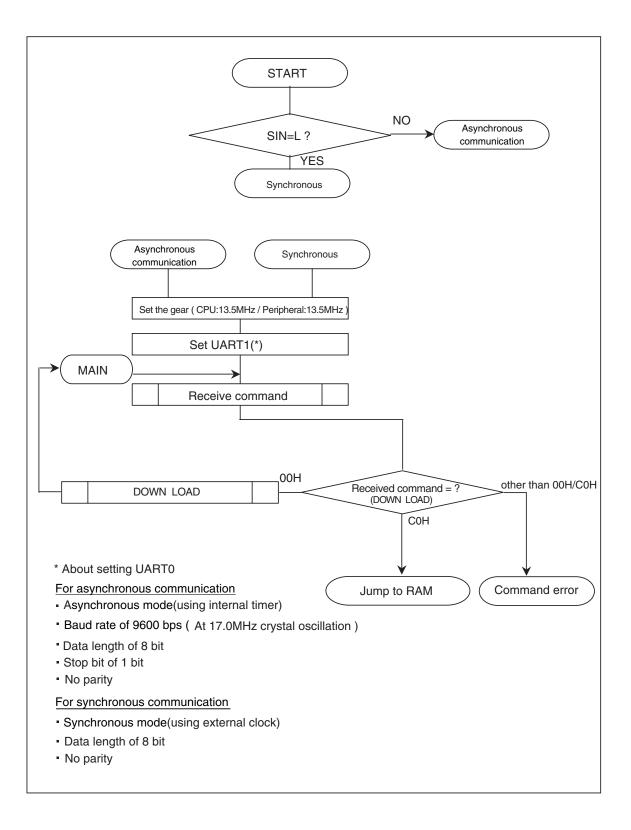

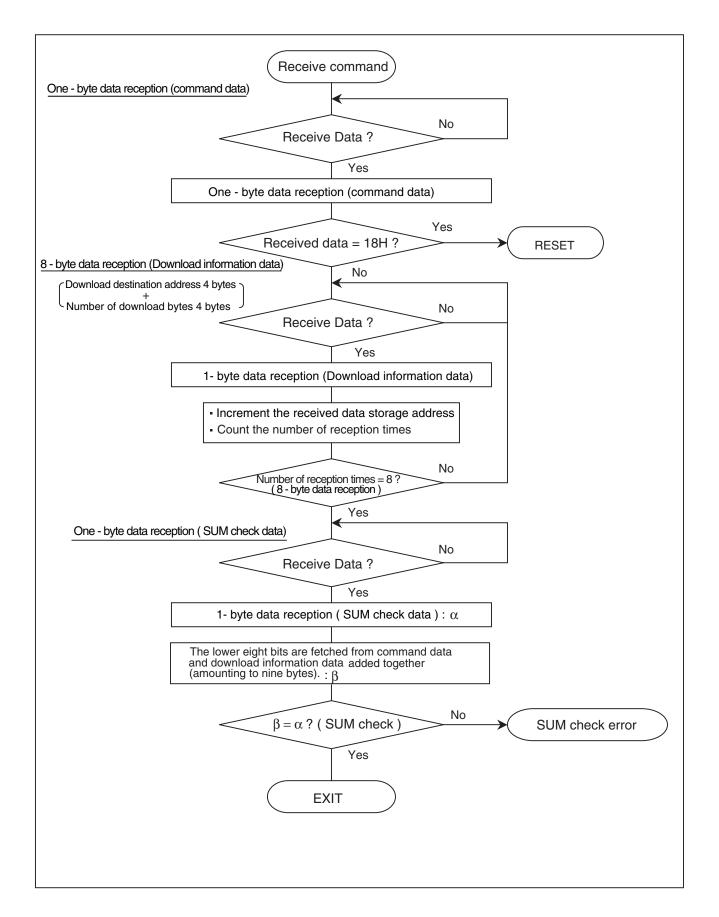

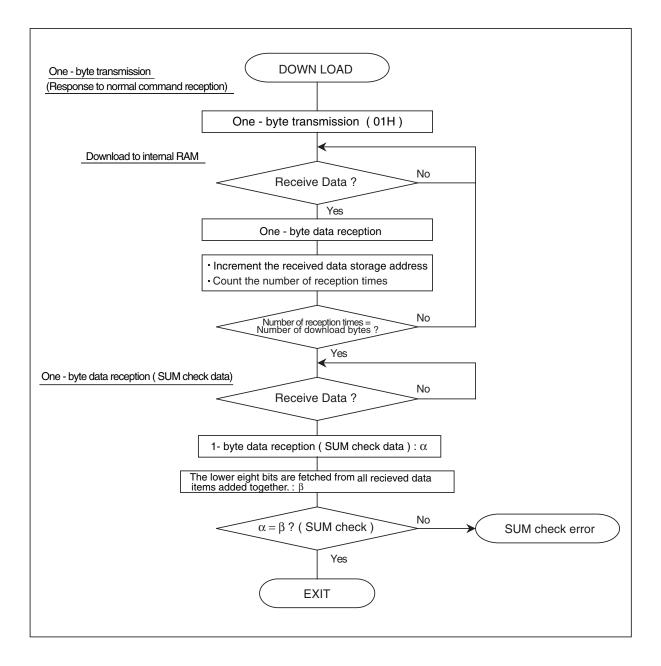

| 32               | 37                 | WR0/<br>DQMUU | C                    |                        | [WR0] External bus write strobe output.<br>This pin is enabled at external bus<br>mode. When WR is used as the write<br>strobe, this becomes the byte-enable<br>pin (UUB).<br>Select signal (DQMUU) of D31 to D24<br>at using of SDRAM. |